基于USB和FPGA的随机数发生器验证平台

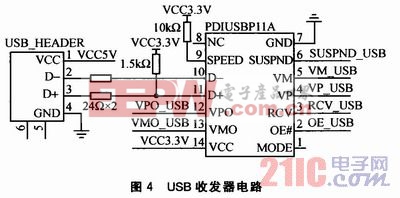

3.2 USB收发器电路

PDIUSBP11A芯片拥有14个可用引脚,其电路原理图如图4所示。

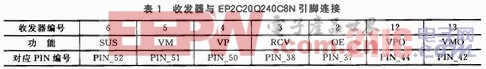

在本设计电路中,将PDIUSBP11A芯片的引脚1和引脚8悬空;引脚7和引脚14分别接地和3.3 V电压;差分数据信号D+和D-引脚分别经一个阻值为24 Ω的电阻与USB接口的D+和D-相连,同时D+经上拉电阻与3.3 V电压相连;引脚9经上拉电阻与3.3 V电压相连,使USB保持在全速工作模式下;其他引脚与FPGA芯片相应的引脚相连接,具体连接方式如表1所列。

3.3 配置芯片及下载电路

Altera编程硬件主要包括MasterBlaster、ByteBlasterMV、ByterBlsterII、USB-Blaster和Ethernet Blaster下载电缆或Altera编程单元(APU)。

本文采用ByterBlsterII下载电缆,选用EPCS4配置芯片,设计实现了AS主动串行配置模式与JTAG下载模式相混合的下载配置电路。

本设计采用AS和JTAG两种下载方式,可以通过JTAG方式对程序进行调试,同时通过QuartuslI软件提供的一个可在线操作FPGA片上RAM内容的工具InSystem Memory Content Editor,用户可以查看和修改RAM的内容。用户可以预期对RAM中的内容进行修改,并通过该工具查看修改后的结果,两者进行对比就可验证程序运行是否正确。此外,在JTAG模式下可以利用jic文件验证配置芯片是否已经损坏。

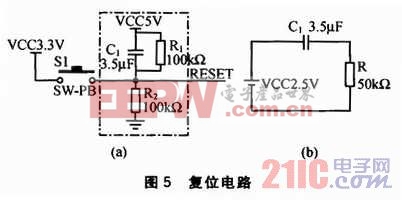

3.4 复位电路

为使验证系统初始化正确,当整个系统在电源上电时,必须处于复位状态。一般应保持复位脉冲为高保持两个机器周期以上,而系统晶体振荡器达到稳定一般需要150 ms左右。为此,本文设计了基于RC器件的复位电路,如图5所示。

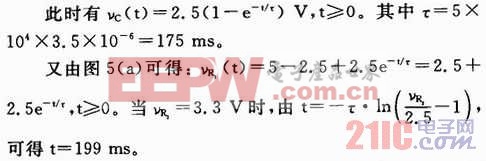

其中,R1=R2=100 kΩ,C1=3.5μF,对于虚线中的电路,运用戴维南定理把系统上电后电路中除电容支路以外的部分进行化简,得到的电路如图5(b)所示。

由此可得,该复位电路能够正常复位,保证系统正常工作。

3.5 时钟电路

时钟由晶振芯片提供,晶振芯片有无源晶振和有源晶振两种。无源晶振为无极性元件,共有2个引脚,只有在时钟电路工作控制下才能产生振荡信号;有源晶振由石英晶体组成,此外还有晶体管和阻容元件,信号稳定,它共有4个引脚,常用的连接方式为:1脚悬空,2脚接地,3脚输出,4脚接电压。本设计采用ELV型号为SMD5*7的48MHz晶振。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码