基于ADS仿真的X波段二倍频器设计

输入匹配电路的设计主要是使激励源与FET输入阻抗实现共轭匹配,保证激励功率中的基波有效的加到FET输入端,同时抑制其他谐波输入和返回激励源,这也是高功率和高效率输出的基础。在距离FET输入端的输入微带线上并联一条对应2ωo的λ/4开路短截线,用来反射二次谐波信号,使输入电路在二次谐波频率上等效阻抗为0,防止二次谐波泄漏至激励源。输入微带线的长度取为2ωo的λ/2,使对于二次谐波频率而言,输入端始终为短路点,可以减小输入电路变化对输出电路的影响。

输出匹配电路是使输出FET阻抗与谐振回路匹配,以获得最大的倍频功率和转换效率。对于FET,基波输出功率与需要的谐波输出功率相差不大,故二倍频设计对基波功率的抑制尤为重要。在距离FET输出端的输出微带线上并联一条对应ωo的λ/4开路短截线用来反射基波信号,即使输出电路在基波频率上等效阻抗为0,输出微带线的长度取为ωo的λ/2,使对于基波频率而言,输出端始终为短路点,可以减小输出电路变化对输入电路的影响。

偏置电路和隔直电容的设计。偏置电路用以提供倍频器合适的偏置电压,直流工作点不仅直接影响输出功率和效率的高低,而且还密切地关系到倍频电路的稳定性,如果设计不当,甚至可能使倍频器完全不能工作。另外,为防止输入/输出偏置电路形成低频空闲回路,在

输入/输出阻抗部分分别加ωo,2ωo的λ/4高阻抗线,以减小偏置电路引起射频信号的泄漏。设计时还需考虑避免直流偏置电路的电源噪声及电阻噪声混入射频通道影响倍频噪声性能,而且电源纹波及噪声可能恶化相位噪声和杂波抑制指标,电源过冲可能损坏内部电路,应使用低纹波的无过冲电源,且直流供电必须足够大且去耦。同时考虑栅极和漏极偏置电压加电时序,以防器件损坏,此外,还要考虑小的附加损耗、寄生振荡的抑制、独立电源供电、反射等,所有这些都应该在实际的调试过程中得到充分的考虑。

2 二倍频器设计与仿真

2.1 晶体管选择

在倍频器设计过程中首先要选择合适的非线性器件作为倍频器件,器件选择主要考虑以下三点:

(1)要充分利用晶体管工作频率的上限,有利于保持电路稳定性,预防自激。

(2)选择非线性强的管子,根据工作状态和激励功率、输出功率的要求挑选直流参数和极限参数符合要求器件。

(3)对于频率很高时,还需晶体管具有较大的Rds和较小的Cgs。

在电路设计中,设计指标是ADS优化设计的关键,即输出功率、效率、倍频增益、带宽等。在Ku频段倍频增益中,考虑的主要技术指标是稳定性、倍频增益和输出功率,从理论上讲,可以选择双极型晶体管和场效应管,但场效应管相对于双极型晶体管有更高的截止频率,工作状态的稳定性也比双极型晶体管好。综合考虑系统指标要求,此次设计采用NEC公司的GaAs MESFET NE900100实现倍频。

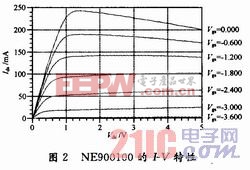

由ADS软件中,由NE900100的等效模型容易得到其I-V特性,如图2所示。从图中可以看出,其固有性能参数如下:夹断电压Vt=-4 V,漏极电流峰值Imax=227 mA,DATASHEET还提供了管子的典型应用状态,Vds=8 V,Idds=90 mA及其小信号S参数。

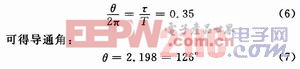

由式(3)可知,对于二次谐波,电流脉冲持续时间的最大值通常选在τ/T=0.35处。由于电流脉冲持续时间与导通角存在如下关系:

![]()

调节漏极电流脉冲持续时间主要反映为栅极偏压的选取,也反映为导通角的选取,即取:

为获得二倍频最大输出功率,选择导通角为126°,对应得到最大二次谐波分量,但同时要注意对基波和三次谐波的抑制。此时主要通过调节栅极偏置来实现短的导通间隔,选择VggVt,使得τ/T=0.35,同时Vgg的选取还必须考虑栅极偏压对峰值反向电压的影响,避免超过击穿电压而损坏管子。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码