基于1553B总线协议的解码器设计和FPGA实现

2 EDA设计

本文设计的ManchesterII型码解码器选择ALTERA公司的Cyclone系列的EPlC6Q240C6芯片作为目标器件,在QuartusII9.0集成环境中,使用Verilog HDL硬件描述语言和原理图混合输入方法实现,使设计简洁有效。

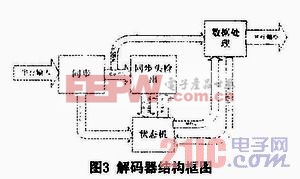

解码器的功能是将1553B总线中串行输入的数据转变成并行数据,并检查数据和奇偶校验位是否正确,为下游的1553B处理器提供正确的数据。如图3所示,解码器包括同步模块、同步头检出模块、数据处理模块、状态机模块。设计采用16M时钟的工作频率。

数据信号和使能信号可以在时钟信号的一个周期之内的任意时间来领,也就是说无法定位数据信号和使能信号对于时钟信号上升沿的时间间隔,这将使各模块内部的时钟计数器无法准确地计时,使状态机无法准确地进行状态跳变。

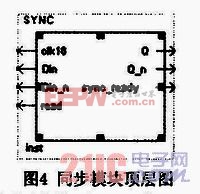

同步模块的作用相当于一个D触发器,它可以使数据信号和使能信号相对于时钟信号的上升沿有固定的时间间隔,这个时间间隔就是同步模块的tco,即时钟输出延时。这样就为下游模块的时钟计算和时序约束提供了一个固定的参数,为各模块的时钟计数器准确计时和状态机正确跳变奠定了基础。

如图4所示,同步模块中Din和Din_n管脚(Din_n为Din的方向输入信号)接收来自1553B模拟收发器的数据信号,read管脚接收模拟收发器发出的使能信号。产生与16MHz时钟的上升沿同步的数据信号和使能信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码