基于千兆以太网的高速数据传输系统设计

TCP/IP协议是一个协议族,集成有数据传输、流量控制、校验、纠错以及管理等多种功能。要通过网络接口实现数据传输,没有必要实现完整的TCP/IP协议,而且在有限的硬件资源上实现整个协议族也是不切实际的。图1为TCP/IP协议族的分层结构,实现数据传输需要在每一层实现一种协议。应用层主要实现用户控制,接收数据以及为发送数据做相应准备等。在运输层,选择UDP协议。UDP协议是面向无连接的,它提供不可靠的传输服务,不保证一定能将数据传输到目的地。而TCP协议是面向连接的,它提供可靠的传输服务,能保证正确的数据传输,协议中包括重传机制、分片机制以及流量控制机制等。但UDP比TCP简单的多,易于实现,占用资源也比较少。在网络层,选择IP协议和部分ICMP协议。IP协议用于数据传输,而ICMP协议用于测试,如ping命令就属于ICMP协议。在链路层,需要有MAC控制器实现以太网数据帧的打包解包、校验和计算等。另外,还需要实现ARP协议。ARP协议用于通知通信双方各自的硬件地址信息。

2 方案选择及实现

2.1 千兆以太网的设计方案研究

千兆以太网的关键技术在于千兆以太网的MAC控制器和以太网接口的实现。目前市场上物理层芯片和MAC芯片都比较多,但大多数MAC芯片是PCI或PCIe接口,这种芯片主要用于计算机主板,而GMII接口的MAC芯片接口简单,便于用户使用。对于不同的系统,设计千兆以太网的方法应根据系统的处理器类型而定,目前主流的处理器有FPGA、DSP、SOC、PowerPC等,根据处理器类型,大致可分为以下3种:

(1)使用FPGA作为主控制器,可以使用一片物理层协议芯片实现物理层,一片MAC芯片实现MAC层,而上层协议在FPGA内部使用硬件描述语言实现。也可以在FPGA内部使用MAC核代替MAC芯片,从而简化系统设计。如Xilinx Virtex-5系列FPGA中就集成有10/100/11 000 Mb·s-1以太网MAC控制器硬核,而Altera提供Triple Speed EthemetMegaCore软核控制器。

(2)使用集成有MAC控制器的DSP芯片,外部使用物理层芯片来实现物理层。如TI公司的TMS320C647x系列DSP,它采用哈佛总线结构,集成

度较高,运算速度快。可以完全使用C语言编程,操作方便。

(3)使用基于嵌入式操作系统的TCP/IP协议栈,如PowerPC芯片,它可以嵌入某些操作系统,如Linux系统,能够方便的实现TCP/IP控制,外部使用一片物理层芯片即可。由于有TCP/IP协议栈的支持,省去了编写协议的工作。

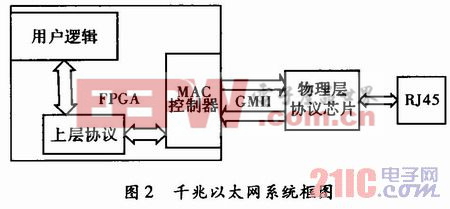

在系统中,主控制芯片选择Altera公司的StratixlI系列FPGA,StratixII系列FPGA片资源丰富,支持多种电平标准,并集成有M4K,M512等多种形式的存储器资源,可以实现数据的缓冲及存储。MAC控制器使用该公司提供的MAC软核来实现,该软核支持多款物理层芯片,选择NI公司的DP83865芯片,系统如图2所示。

此方案较其他方案有明显的优势。(1)DP83865采用GMII接口,简单易用,而且性价比很高,与Altera公司的MAC软核一起使用上简化了设计者的工作,能有效缩短产品开发周期。(2)MAC软核在FPGA内部占用的逻辑资源较少,所以并不会增加系统的额外开销。

2.2 物理层芯片介绍

DP83865支持10Base-T/100Base-Tx/1000Base-T以太网协议,它使用0.18 μm、1.8 V CMOS工艺,使用MII、GMII或RGMII的媒体独立接口,简化了与MAC控制器的连接,具有超低功耗、完全自适应等特点,便于用户实现10/100/1 000 Mb·s-1以太网。芯片内部设有32个寄存器,可以通过MDIO接口访问其内部寄存器。Altera公司的MAC软核内部映射有两个物理层芯片的寄存器组空间,其地址空间与DP83865内部寄存器一一对应,用户可以通过访问MAC软核内部寄存器以达到访问DP83865的寄存器目的,MAC软核将自动通过MDIO接口访问DP83865的寄存器。这样,如果要重新设定DP83865内部寄存器值,或者在调试过程中要通过读取寄存器来判断芯片的工作状态,可以直接访问其在MAC软核内部映射的寄存器空间,从而简化设计。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码