一种高速数据采集卡的设计与实现

摘要:为了实现对武器系统模拟信号的采集和数据分析,根据PC/104总线的数据采集系统的设计思想,数据采集卡以A/D转换器、CPLD和FIFO相结合来实现信号的连续采集与数据传输的控制。A/D转换器实现信号的采样保持和模数转换,CPLD实现数据采集和存储过程的控制。实验结果表明,该数据采集卡操作简单、实时性强、性能稳定,可实现对被测信号高速连续的数据采集。

关键词:数据采集;复杂可编程逻辑器件;FIFO;时序控制;逻辑控制

O 引言

测试设备是武器系统中最主要的子系统之一,它的工作正常与否将直接影响到整个武器系统的作战性能。在对武器系统进行测试的过程中,需要对一系列的电压、电流等模拟量信号进行快速、实时的数据采集和分析,检查这些模拟量的指标是否符合要求,可以对武器系统是否发生故障做出诊断,保证武器系统的正常工作。根据现代战争对武器系统的作战需求,提高快速机动保障能力,研制出体积小、结构紧凑、便携式的测试设备就成为主要的目标。

本文设计了一种基于PC/104总线的高速数据采集系统,其目的在于替代示波器在武器系统测试中的作用。常规采集方案主要有两种:

(1)由单片机直接控制的采集方案,这是最简单最常用的控制方案。由于每次采样都要有单片机的参与,需占用单片机的时间,影响其数据处理,而且对于多通道、多个A/D转换器的控制,因所需处理的信息更多,则更加不方便。

(2)由DMA控制的采集方案。此方案硬件电路复杂,若与单片机配合使用,需要单片机具有总线挂起功能,否则还需要进行总线切换,影响数据的及时处理。

综合以上两种方案的优缺点,本数据采集卡自动采样硬件电路主要采用可编程逻辑器件CPLD和先进先出FIFO(First In First Out)技术设计而成,可以很好地实现高速数据采集。

1 数据采集卡总体方案设计

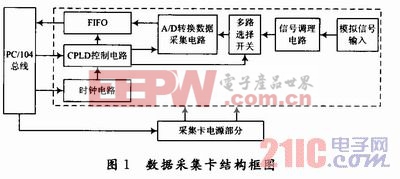

数据采集卡是由信号调理电路、带采样保持器的A/D模数转换器、多路模拟开关、FIFO数据缓存、CPLD芯片及时钟电路等部分组成,具有高精度、高可靠性、高抗干扰能力等特点。总体结构设计原理如图1所示。

2 芯片介绍

该数据采集卡采用的芯片主要有:AD9283模/数转换器、AD508A多路选择开关、EPM7128SCL84-6CPLD和CY7C4261 FIFO缓存器。下面对以上所用芯片做一简要介绍。

2.1 AD9283模/数转换器简介

本数据采集卡选用了ANALOG DEVICE公司生产的高速8位模/数转换器AD9283。它采用先进CMOS制作工艺,提供20脚表面贴装封装形式。片内集成高性能采样和保持放大器,输入信号可采用单输入或差分输入;处理输入电压峰峰值在0~1 V之间的模拟信号;采用单+3 V模拟电源和单+3 V数字电源;片内提供+1.2~+1.3 V的参考电压;最高抽样速率可达100 MSPS;具有高速并行输出接口。

2.2 EPM7128SCL84-6 CPLD芯片简介

本数据采集卡选用一片Altera公司生产的EPM7128SLC84-6CPLD作为核心处理芯片,它具有高阻抗、电可擦除等特点,可用门单元为2 500个,有64个用户可用I/O引脚,工作电压为+5 V,管脚间最大延迟为5 ns,采用PLCC-84封装,通过JTAG接口可实现在线编程。

2.3 CY7C4261 FIFO缓存器简介

本数据采集卡选用的FIFO器件是CYPRESS公司生产的高速、低功耗、先入先出存储器芯片CY7CA261。它的容量为16K×9位,读写周期为10 ns,支持异步和同步读写操作,写数据和读数据分别具有时钟和使能信号,具有“空、满、可编程几乎空、可编程几乎满”四个状态标志位,没有绝对地址的概念,只有读指针和写指针的相对位置,只要标志不为0,就可以进行写操作,只要标志不为0,就可以进行读操作,读写操作可以同时进行。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码