基于FPGA的视频采集与显示模块设计

3 参数设置

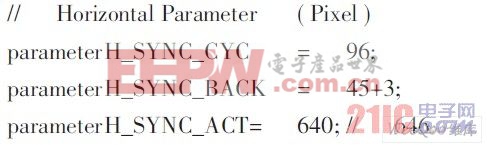

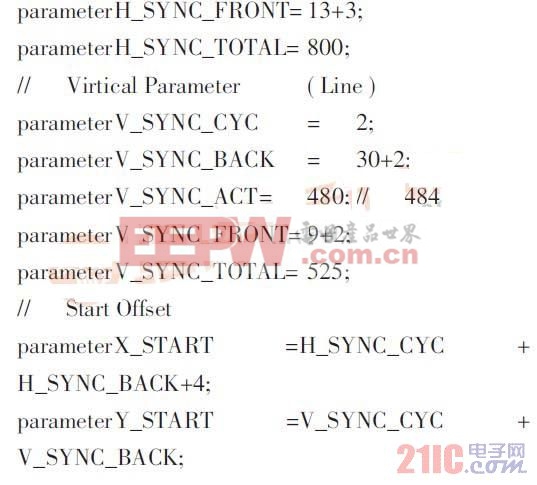

本系统采用640×480 像素显示, 刷新率为60Hz模式, 像素时钟为25MHz。在VGA水平时序中, 每行包括800像素点, 其中640为有效显示脉冲, 160为行消隐区; 而在VGA垂直时序中, 每场525行, 其中480有效, 45行为场消隐。其具体参数如下:

4 结束语

本文介绍的图像采集和显示模块设计简单,成本较低。由于其用高效硬件描述语言构成, 故其处理效率高, 具有很好的实用特性。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码