基于FPGA的语音存储与回放系统设计

2.3 模数转换(ADC)电路

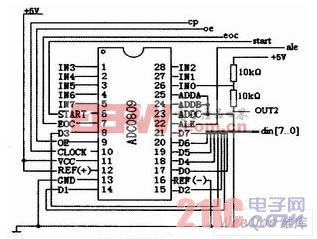

ADC电路如图4所示。题目要求采样频率fs=8kHz,字长=8位,可选择转换时间不超过125 μs的8位A/D转换芯片,ADC0809的转换时间为100μs,可选用ADC0809。音频信号经过放大、滤波送给ADC0809 ADC电路,将模拟量转换为数字量,再经可编程器件送给存储芯片。cp、oe、eoc、start、ale、din[7..0]接图9。

图4 ADC电路

2.4 语音存储电路

存储芯片HM628128D管脚如图5所示。HM628128D可存储8位131072字,5V供电,静态RAM。语音存储时间≥10s。HM628128D在数字化语音存储与回放系统硬件电路中的接线如表1所示。HM628128D读写功能如表2所示。

图5 HM628128D管脚

2.5 数模转换(DAC)电路

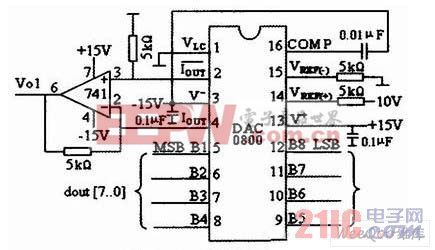

DAC如图6所示。题目要求变换频率fc=8kHz,字长=8位,可选择转换时间不超过125μs的8位D/A转换芯片,DAC0800的转换时间为100ns,可选用DAC0800。存储芯片输出的数字量经可编程器件图9送给DAC0800 DAC电路,将数字量转换为模拟量。

图6 DAC0800 DAC电路

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码