LZW改进压缩算法的FPGA实现

传统的LZW压缩算法采用8位数据输入,固定长度编码输出,随着字典内容的不断增多,输出编码的位数不断增加势必造成资源的浪费,也会损失压缩率。另外,由于字典的容量有限,随着压缩过程的进行,字典会被填满,若是简单的不再向字典中增加内容,那么后面的压缩率就会降低,而如果将字典全部清除重新建立字典,在字典建立初期压缩率也是很低的。针对以上不足,文献对LZW算法做以下改进:采用12位数据作为压缩输入,变长度的码字输出。

压缩字典最多可容纳16 384个码,共分为三部分,其中0~4 095为12位输出,4 096~8 191为13位,8 192~16 383为14位。每当输出长度变化时,同时输出一个变长标识,便于解码器解码。

2 LZW算法FPGA实现

2.1 算法实现硬件结构

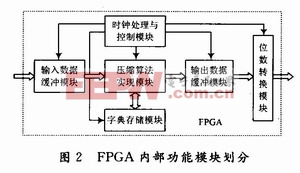

LZW数据压缩算法的FPGA硬件实现,其内部功能模块划分如图2所示。

2.2 各功能模块说明

输入/输出数据缓存模块完成FPGA所有数据传输工作,为了保证异步时钟域数据同步,使用FPGA片内的Block RAM构成一个FIFO对输入数据进行缓存。

字典存储器模块需要存放字典项的三部分内容:字典项编码、前缀码、当前码。将存储器的容量设计为1K。采用FPGA内部宏单元lpm-ram-dp(单口RAM)设计字典存储器。

算法实现模块要实现匹配串的查找、判断字典相应地址内容是否为空、比较字典地址相应内容是否匹配或冲突、冲突时重新生成地址、压缩编码输出控制、压缩结束控制等功能。

外接闪存数据宽度为8位,所以压缩后输出数据位数需要转换。数据转换模块就是实现压缩后数据由13位向8位的转换。

时钟处理与控制模块主要完成时钟的匹配与控制,对各个功能模块分配时钟,并初始化各使能端信号。

2.3 仿真结果

清空字典存储器模块,初始化信号,将可能出现的单字符存入字典,压缩时新传续存地址为4096,新字符串输入时产生相应的哈希表地址与偏移量;然后读字典存储器相应地址的内容,如内容为空则输出输入的数据,并把相应内容存入字典,如内容匹配,则继续输入下一数据,否则(即发生冲突)产生新的哈希表地址,重新读取字典,进行判断、比较。仿真时序如图3所示。

仿真结果:输入数据为5,6,7,8,9,5,6,7,8,9,5,6,7,…;输出数据为5,6,7,8,9,4 098,4 100,4 102,…。仿真结果与理论计算值一致。

3 结 论

LZW算法逻辑简单,实现速度快,擅长于压缩重复出现的字符串;无需事先统计各字符的出现概率,一次扫描即可;相对于其他算法,更有利于硬件实现。本文利用FPGA实现了改进的LZW压缩算法,仿真证明其算法具有很高压缩率,适合工程的实际应用。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码