LVDT数字解调方法研究

2 硬件结构

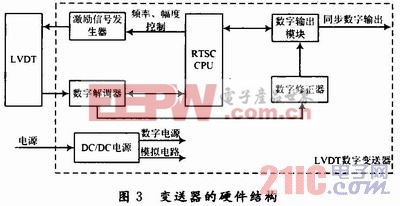

变送器的硬件主要包括处理器、激励信号发生器、闪存工作状态控制器、闪存和SRAM存储器、主动配置芯片、通信接口、显示屏和键盘以及电源、时钟/复位。如图3所示。

具体实施方法参见图3,测量过程如下:

首先,通过激励信号发生器产生正弦波数据,其频率和幅度由配置存储器中的控制字控制,激励信号送至LVDT,LVDT的次边信号送至数字解调系统,解调的结果送数字修正器进行误差修正和必要的滤波,误差修正数据存储在FPGA片外的误差表ROM存储器。修正后的结果送数字输出模块,以同步方式对外输出。数字输出同时送至模拟输出模块转换成模拟信号输出。

校准工作过程:首先将变送器设置为校准状态,每得到一个数据点,测出其铁芯的真实位移值,通过多点的测量来得到其线性系数,校准工作在整个量程内逐点进行,上位机根据所得数据,通过线性插值算法计算误差修正表,通过处理器写入误差修正表ROM存储器。在整个量程内的校准点越密集,所得误差修正表越精确。

3 软件设计

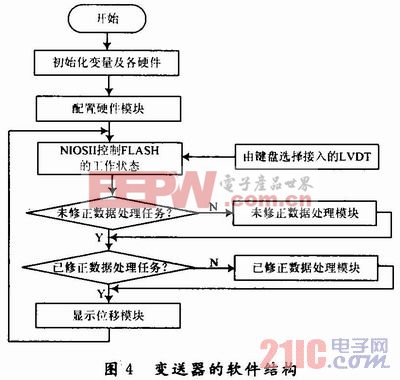

变送器软件是指运行于“LVDT数字变送器”中FPGA内的处理器平台之上的软件。变送器软件有3大功能:控制变送器各个部分的协同工作;与PC通信,对变送器配置、校准,采集位移数据;通过变送器的人机界面接收用户的各项指令。变送器软件采用“前后台系统”实现各任务的调度和资源分配,以提高任务级响应的实时性,同时“前后台系统”不增加额外的软件代码和处理器执行时间,留出更多的内存空间用于存放采集的实时位移数据。当上位机和FPGA启动时,首先要进行初始化,并对硬件进行配置,使其能正常的工作,由处理器来控制闪存的工作状态,此时LVDT接入系统,对未修正数据进行修正处理,最后得出准确的位移值,呈现于显示模块,如图4所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码