基于0.5μm CMOS工艺的一款新型BiCMOS集成运算放

2 电路仿真

Aod是在标称电源电压和规定负载下,运算放大器工作在线性区,低频无外部反馈时的电压增益,Aod的值越大越好。图4为输入端V+的电压波形。由图可见V+的峰峰值为200 nV,输入端V-的电压为0。图5为输出波形(在Q3的集电极输出)。

满足设计要求。

3 版图设计

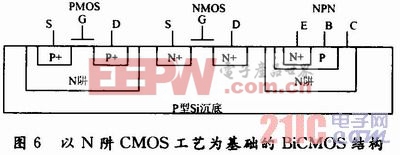

采用的是以CMOS工艺为基础的BiCMOS兼容工艺。首先以外延双阱CMOS工艺为基础,在N阱内增加了N+埋层和集电极接触深N+注入,用以减少BJT器件的集电极串联电阻阻值,以及降低饱和管压降;其次用P+区(或N+区)注入,制作基区;再者发射区采取多晶硅掺杂形式,并与MOS器件的栅区掺杂形式一致,制作多晶硅BJT器件。由此可见,这种高速BiCMOS制造工艺原则上不需要增加其他的重要工序。

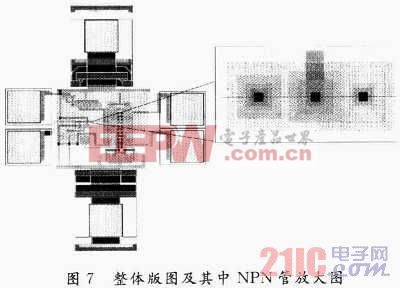

由于基准电路不易调整,在设计版图时将基准部分外接。基于0.5μm CMOS工艺的运算放大器版图如图7所示。

4 结语

该运算放大器结合了CMOS工艺低功耗、高集成度和高抗干扰能力的优点,双极型器件的高跨导,负载电容对其速度的影响不灵敏,从而具有驱动能力强的优点。该BiCMOS器件在现有CMOS工艺平台上制造。该放大器以CMOS器件为主要单元电路,在驱动大电容负载之处加入双极器件的运算放大器电路,然后在Tanner Por软件平台上完成电路图的绘制、仿真,并在MCNC 0.5μm CMOS工艺线上完成该电路的版图设计,经实用,运算放大器的参数均达到了设计要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码