基于FPGA的雷达中/视频数据采集与回放系统设计

3.1.1 数据采集模块设计

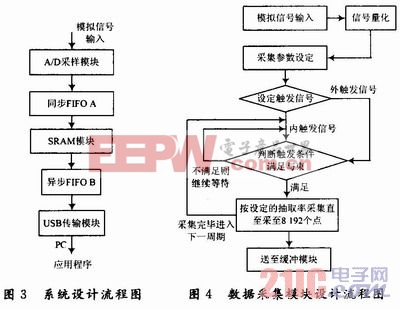

雷达信号采集技术中,采集时序控制与实时数据传输是关键也是技术的难点所在。为保证采集的连续性,设计中采用了FPGA内部双FIFO的缓冲技术、外置专用缓冲芯片技术与计算机公用缓冲区环行存储技术。该模块的详细软件设计流程如图4所示。

3.1.2 数据缓冲模块设计

数据缓冲模块设计了同步FIFO A和异步FIFO B。其中FIFO A的一端接收A/D转换数据,另一端将数据传输给外部SRAM;FIFO B的一端接收SRAM的数据,另一端将数据传输给USB单片机的FIFO。

3.1.3 测频模块设计

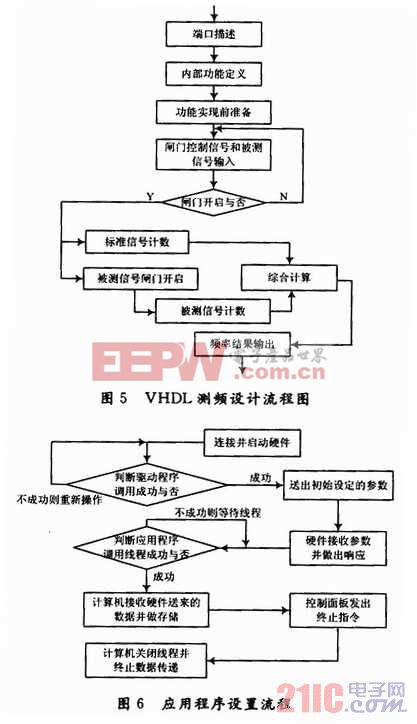

基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测量精度。综合考虑,本系统采用等精度频率计的测量方法。其基本流程图如图5所示。

3.1.4 测电压模块设计

采集信号经A/D变换器量化编码以后,可以根据量化得到的结果进行信号幅度值的计算。同时考虑到采集到的信号尤其是正弦波、三角波等信号在测量时会发生抖动,所以在进行电压测量时,采用了取平均值和对信号进行平滑处理相结合的方法提高测电压的精度,设计实现对信号峰峰值、平均值的测量。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码