基于Altera FPGA的千兆以太网实现方案

整个配置界面可将IP核配置为所需模式并进行IP核参数设置,将IP核设置为千兆以太网MAC模块,内部提供FI—FO模块。可选的PCS模块由PHY器件提供,这个界面分为4个配置页面,描述如下:

- Core Configuration:核配置选项,配置以太网功能模块,是否包含PCS模块、FIFO模块,配置接口类型、端口数等;

- MAC Options:MAC配置选项,配置MAC模块功能;

- FIFO Options:FIFO存储器选项,可设置FlFO存储器类型以及存储器数据长度;

- PCS/SGMII Options:物理介质接入层模块配置页面,配置物理层。

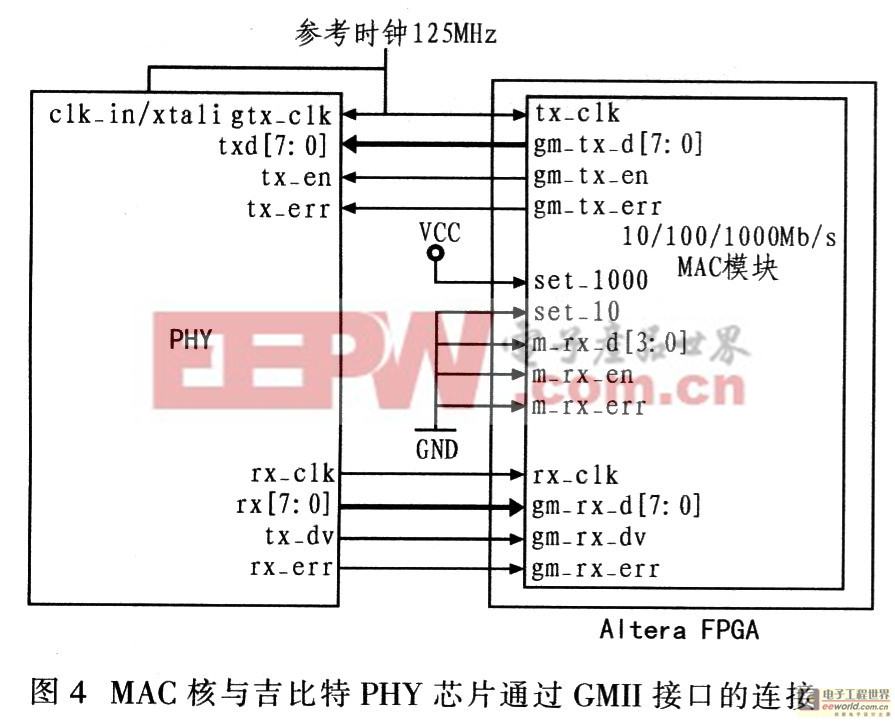

相应的接口信号包括:控制接口信号,复位信号,MAC系统端信号(包括接收接口信号和发送接口信号),MAC以太网端信号(包括GMII模块信号和PHY管理接口信号)。

表1中描述了MAC以太网端GMII模块信号、接口信号,其余信号参考千兆以太网用户手册。GMII模块的接收信号一般直接连到PHY器件,负责与PHY器件的数据交互,其信号与PHY器件接口一一对应,如表1所列。

4 物理层(PHY)器件

Ahera公司的千兆以太网MAC核默认支持的物理层器件有支持10/100 Mb/s的National DP83848C,支持10/100/1 000 Mb/s的National DP83865,Marveil 88E1145以及支持双物理层和10/100/l 000 Mb/s的Marvell 88E1111。在此,选择National DP83865为PHY器件。

MAC核与吉比特PHY器件通过GMII接口的连接如图4所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码