一种基于CMOS工艺的电荷泵锁相环芯片的设计

锁相环路(PLL)是一种能够跟踪输入信号的闭环自动相位控制系统,其理论基础为自动控制理论。锁相环具有载波跟踪特性,可提取淹没在噪声之中的信号,制成高性能的调制器和解调器;用高稳定度的振荡器做参考频率,可提供一系列频率高稳定的频率源,可进行高精度的相位与频率测量等。在模拟与数字通信系统中,锁相环已成为不可缺少的基本部件。随着大规模集成电路技术的发展与成熟,CMOS工艺以其低成本、低功耗、高集成度的优点使得采用CMOS工艺实现高性能集成锁相环具有十分重要的意义和广阔的前景。采用电荷泵结构的锁相环以其易于集成、低功耗、低抖动、无相差锁定等优点,得到了广泛的应用。

2 电路设计

锁相环能够实现两个电信号的相位同步、频率相同或倍频。如图1所示,锁相环由4个基本部件即鉴相器、电荷泵、低通滤波器和压控振荡器组成。鉴相器作用是对两个输入信号进行比较,输出一个正比于这两个输入信号相位差的直流电压,即一个上升或下降的脉冲信号,这个直流电压又作用于下一级电路即开关电荷泵,然后,电荷泵将鉴相器的输出信号放大,给低通滤波器的电容充放电。而环路低通滤波器是用来滤除鉴相器输出误差电压中的高频分量,起到滤波平滑作用,以保证环路稳定以及改善环路跟踪性能和噪声特性。最后,压控振荡器依据传输过来的控制电压来改变输出信号的频率和相位,因此整个系统就形成了一个反馈系统,最终压控振荡器的输出信号锁定在参考信号的频率和相位上。

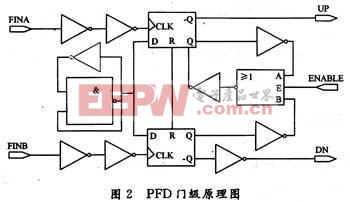

2.1 鉴频鉴相器

鉴频鉴相器是一个相位比较装置,用来检测输入信号相位与反馈信号相位之间的相位差,其结构如图2所示。PFD比较输入信号FINA和FINB的上升沿。当信号FINA的上升沿超前于信号FINB的上升沿时,PFD的输出信号UP被置为1,而输出信号DN为0,当FINB的上升沿到来时,UP变为‘0’,DN 是窄的脉冲;反之,当信号FINB的上升沿超前于信号FINA的上升沿,PFD的输出信号DN被置为‘1’,而输出信号UP保持‘0’,当FINA的上升沿到来时,DN变为‘0’,UP是一很窄的脉冲。信号UP或DN被置为高电平的时间长度等于信号FINA与FINB的相位差。当环路锁定时,PFD的输出信号都保持在低电平。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码