多相滤波的数字相干检波原理及FPGA实现

设原型滤波器的冲击响应为h(n),由(1)式知,其多相结构第K条支路的冲击响应为

则EK(z)频率响应为

令D=4,则式中除i=0项不为零外,其余均为零,所以求得

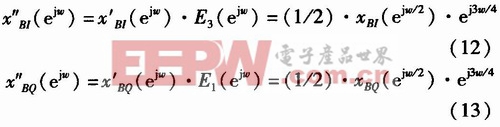

提取K=3及K=1作为式(7)及式(8)I、Q两路延迟滤波,得

由此可见,经过

2 仿真分析

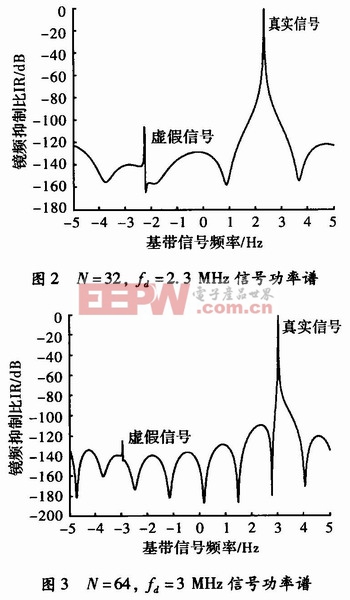

下面采用多相滤波的方法对带宽B=5 MHz,载频fo=60 MHz,信号频率fd的带限信号直接中频采样提取正交的基带分量,采样频率fs=80 MHz,依照多相滤波原理,设计阶数为N,截止频率为B的FIR原型低通滤波器,并从中抽取出数字谱相差

从数据中可以看出,原型滤波器阶数n越大,镜频抑制比IR越高,fd越大,镜频抑制比IR有下降趋势。图2和图3分别表示N=32,fd=2.3 MHz的及N=64,fd=3 MHz的带限信号相参处理后的功率谱分析。

对于N=32,fd=2.3 MHz的带限信号镜频抑制比IR高达106.14 dB,可见结合带通采样定理及多相滤波方式实现对带限信号直接中频采样获取基带信号能够达到很高的镜频抑制比,这是传统的模拟相干检波难以实现的。

如上文所述,对宽B=5 MHz,载频fo=60 MHz的线性调频信号直接中频采样,利用多项滤波的方式实现数字下变频仿真输出波形,如图4所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码