基于FPGA的高速宽带跳频发射机的中频设计

2.3.3 并串转换

并串转换通常应用在FPGA内部单路串行处理速度不能满足要求的情况下,需要使用多路并行低速模块实现高速处理,属于资源与速度互换的一种应用。本设计需要用800MSPS与DAC接口,而FPGA内部最高频率仅为250M左右,所以在FPGA利用并行4路,每路200MSPS,实现串行800MSPS的处理能力。这就需要在输出时需要进行并串转换。利用ALTERA提供的LVDS模块可以很容易的实现并串转换。

2.4 测试与验证

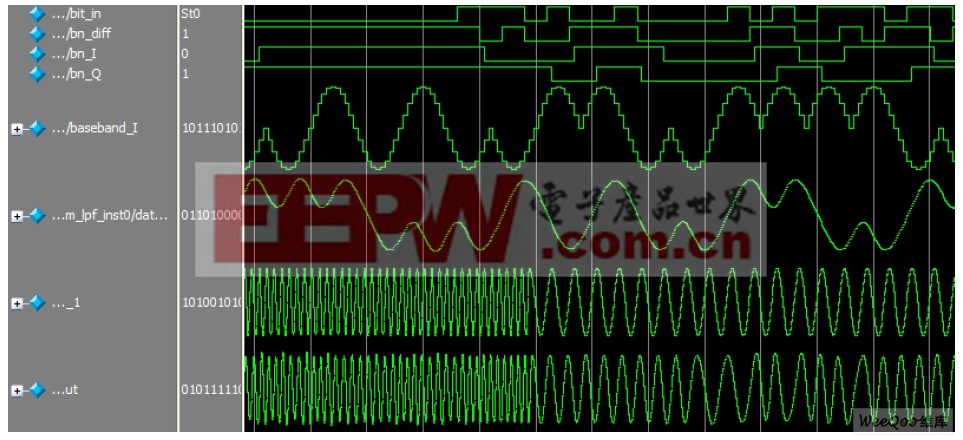

完成各个模块设计和仿真验证后,在顶层文件中调用各个子模块,实现一个完整的MSK宽带跳频发射机。在Modelsim中进行功能仿真的波形如图5所示。

图 5 跳频发射机系统Modelsim仿真波形

图5中从上到下的信号分别为:码元输入 ;差分编码输出;串并转换后I路输出;串并转换后Q路输出;基带调制后I路输出,I路内插到4路并行200MS/S数据速率时,其中1路输出;4路并行NCO,其中1路输出;MSK调制输出。

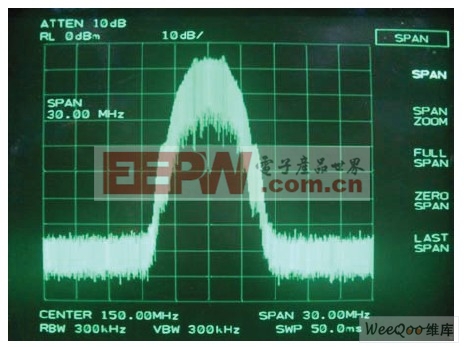

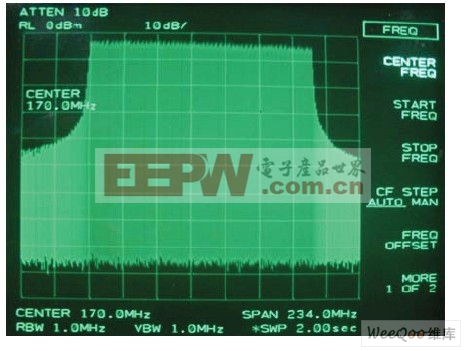

编译完成后将程序下载到跳频发射板,使用HP8563e频谱仪观察产生信号频谱,如图6和图 7所示。

图6为单频点MSK调制频谱图。图中中心频率为150MHz,屏幕显示带宽为30MHz。从图中可以看出经成形后的MSK频谱带宽为10MHz左右,带外衰减大于60dB。满足设计要求。

图7为跳频频谱图。跳频频率范围为95MHz ~ 255MHz。其*51个频点,相邻频点中心频率间隔为3MHz。由于FPGA输出数据速率为800MSPS,所以工程上可实现320MHz带宽。

图 6MSK单频点频谱图

图 7跳频频谱图

本设计给出一种通用软件无线电跳频发射机的硬件平台,以及基带和中频信号处理算法。对于研究FPGA在软件无线电跳频发射系统中的应用具有现实意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码