一种基于FPGA的多时钟片上网络研究与设计

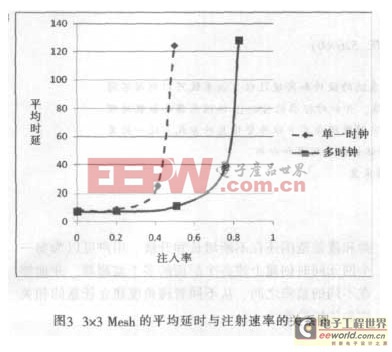

为了*估所设计的多时钟架构的性能, 将利用所设计的路由器的VHDL 模型,模拟一个3×3Mesh 结构,在本身频率下执行包装产生的数据包。路由器的频率值会在拓扑结构合成,布局和布线阶段完成之后得出。对于不同的配置(资源的可用性、跨路由器的距离、bRAM/dRAM FIFO 的版本),路由器的频率可以降低高达18%[6]。图3 显示了单一时钟与多时钟,在延时与注射速率关系中的曲线图。在单一时钟时,网络的频率为286MHz。而在多时钟时, 频率的范围是从286MHz~357MHz。图3 中,X 轴表示的注射率是在一个周期内每个节点注入flit 的数量。Y 轴曲线测量的是每个实例中数据包的平均延时。可以看出,所提出的多时钟片上网络相比单一时钟片上网络的性能显着增加。

4 结语

本文介绍了一个基于FPGA 的高效率多时钟的虚拟直通路由器,通过优化中央仲裁器和交叉点矩阵,以争取较小面积和更高的性能。同时,扩展路由器运作在独立频率的多时钟NoC 架构中,并在一个3×3Mesh 的架构下实验,分析其性能特点,比较得出多时钟片上网络具有更高的性能。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码