高速高精度流水线模数转换器的设计

第二版芯片所做改进及测试结果

第二版芯片对第一版芯片参考电压电路的版图进行了修正,如图5所示,本来第1级DAC的参考电压是从节点2和3引入的,现在改成从第2级的参考电压上接入,即从节点1和4上接入,这样ADC各级电路DAC的参考电压均相等。

如图6所示,在15.5MHz输入信号频率和20MHz采样率下测得DNL和INL分别为-0.22/+0.21LSB和-0.62/+0.46LSB.

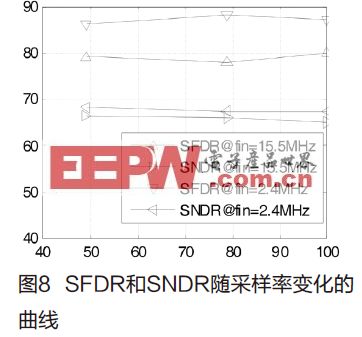

图7是在15.5MHz输入,100MHz采样率的情况下测得的32768点FFT频谱图,由图可知,SFDR达到了79.8dBc,SNDR为65.1dB,有效位数ENOB为10.5bit。

图8给出了SFDR和SNDR随采样率变化的值,在2.41MHz输入信号时,SFDR在100MHz采样率范围内均保持在86dBc以上,而ENOB均大于10.9bit;对于15.5MHz的输入信号,SFDR保持在78dBc以上,而ENOB从50MHz采样率时的10.8bit降到了100MHz采样率时的10.5bit。

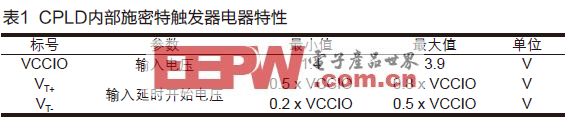

图9是该芯片的显微照片,表1列出了第二版芯片的关键指标。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码