基于FPGA的IRIG-B(DC)码产生电路设计

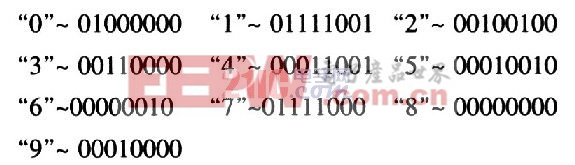

选择EPlC6T144的37引脚作为异步串行输出引脚,与MAX3232E的lO引脚(T2IN)连接,将从FPGA出来的TTL电平转换为串行输出电平从7引脚(T20UT)输出,串行电平转换器采用MAX3232E。选择EPlC6T144的4l、42引脚作为2路IRIG-B码信号输出,因为IRIG-B(DC)码采用RS422电平输出,而从EPIC6T144的4l、42引脚输出脉冲是TTL电平,所以必须进行电平转换,本设计采用TI公司的AN26LS31CD差分驱动器。采用8段数码管作为时间显示器件,显示的信息有天、时、分和秒,共需9个器件,每个8段数码管的0~9个数字显示逻辑为:

3 系统软件程序设计

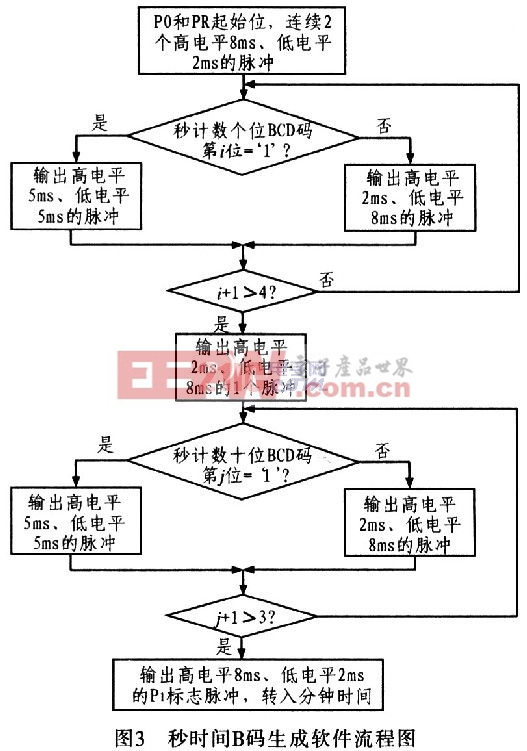

使用VHDL硬件描述语言进行编程,编译环境采用Altera公司的QuartusII7.1。根据图1所示B码脉冲序列宽度图谱,以秒的B码串产生为例。说明VHDL编程设计过程,流程图如图3所示。分、时和天的软件设计根据图l所示的B码示意图,参考秒的设计流程来设计,将100个码元对应的脉冲串按照图l的脉冲宽度输出,就形成整个一帧IRIG-B(DC)码的脉冲串。

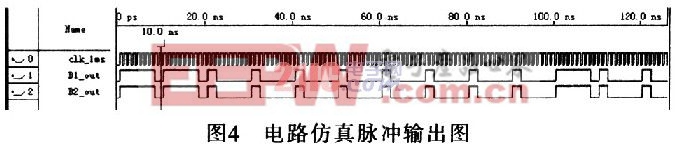

4 电路仿真

电路仿真脉冲输出如图4所示,图中Bl_out和B2_out是IRIG-B(DC)码的输出脉冲,clk_lms是根据晶体振荡器输入脉冲而产生的模拟l ms信号脉冲,可以看出,当连续8个elk_1ms的脉冲时,Bl_out和B2_out保持高电平,即保持了8 ms的高电平,后面的脉冲都严格的遵守图l所示的IRIG-B(DC)码的规则。

5 结论

通过仿真和实际使用表明,该设计电路所产生的IRIG-B(DC)时间码稳定、连续、准确,电路板功耗低、成本低,操作灵活简单,在测控领域有广阔的应用前景。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码