基于Xilinx FPGA的千兆以太网及E1信号的光纤传输

千兆位以太网利用原以太网标准所规定的全部技术规范,其中包括CSMA/CD协议、以太网帧、全双工、流量控制以及IEEE 802.3标准中所定义的管理对象。千兆位以太网的关键技术是千兆位以太网的MAC层和以太网接口的实现。

1 GMII (Gigabit MII)

GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mb/s。同时兼容MII所规定的10/100Mb/s工作方式。接口信号定义如表1所示。

表1 GMII接口信号定义

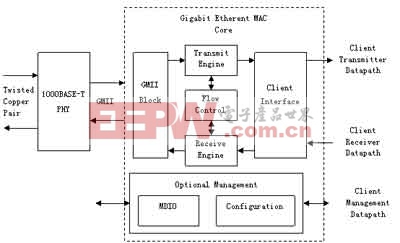

2 Virtex-5以太网媒体接入控制器

在Virtex-5 FPGA中,以太网媒体接入控制器(以太网MAC)模块提供了专用的以太网功能,它和Virtex-5 RocketIO GTP收发器以及SelectIO技术相结合,能够让用户与各种网络设备进行连接。在Virtex-5器件中,以太网MAC模块作为一个硬件块集成在FPGA内部。吉比特以太网MAC功能框图如图3所示。

图3 吉比特以太网MAC功能框图

(1)客户端接口

发送器的客户端接口将帧传送给以太网MAC。当接收到的数据小于最短的以太网帧长度时,发送器将该数据加长,并且保持最小的帧间距;可以增加间隔的长度,还可以通过配置发送器在帧中添加一个帧检验序列。一个单独的流控制接口允许你生成暂停帧。在半双工模式下,信号发送之间存在冲突,在有效冲突情况下,需要进行帧重发。

接收器接口检验传入帧和信号帧误差。这里分别提供了好帧信号和坏帧信号。还可以通过配置以太网MAC以便在检测到有效的暂停帧之后,暂停和重新启动帧传输。

客户端接口的数据的宽度通常是8位或者16位。8位接口主要针对标准的以太网应用,它利用一个125MHz的时钟产生1000Mb/s的数据传输速率。当使用16位模式时,可以在不提高客户端接口时钟频率的条件下将数据传输速率提高到2000Mb/s。

(2)控制接口

每个以太网MAC有一个可选的管理数据I/O(MDIO)接口。它允许对外部PHY的管理寄存器和以太网MAC中PCS/PMA内部的物理接口管理寄存器进行访问。

3 Virtex-5以太网MAC封装

图4显示了一个HDL封装的模块结构图,它可以从Xilinx的CORE Generator工具中获得。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码