FPGA在频率综合器中的应用设计与电路

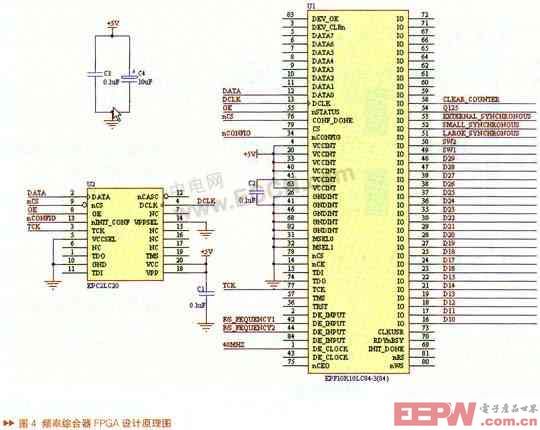

频率综合器的FPGA设计原理图

因为EPF10K10是RAM型器件,设计程序需固化在外部串行自举器件EPC2里,在上电时,PF10K10把设计程序从EPC2读入RAM并运行。频率综合器的FPGA设计原理图见图4。

频率综合器输出信号

频率综合器的核心FPGA控制着锁相环1、锁相环2和开关调制器,使频率综合器工作在不同的状态。

跳频模式

工作在跳频模式时,频率综合器输出信号有跳频同步、外同步、小同步以及大同步。

射频信号:

1路输出:1000-1504MHz,每步跳8MHz,一个周期共64步,后接开关,脉宽120nS,开断>85dB,上升沿5nS,插损2.8dB;2路输出:900-1404MHz,每步跳8MHz,一个周期共64步。点频模式1、2工作在点频模式时,频率综合器输出信号有外同步、小同步和大同步。工作在点频模式时,频率综合器锁定在一个频率点上,点频模式1和点频模式2工作方式相同,只是脉冲重复周期不同。点频模式时,跳频同步不存在,但是外同步可调仍然需要,小同步脉宽变为500nS,脉冲重复频率为50kHz。

同步控制信号

大同步信号:周期为3.15mS的矩形脉冲,前后沿抖动8nS。

跳频同步信号:脉宽120nS,周期为25μS,前后沿抖动8nS。

小同步信号:脉宽120nS,周期为25μS相对于跳频同步脉冲延时10μS,前后沿抖动8nS。

外同步信号:与小同步信号相同,并且延时可调,作为脉冲放大器的时钟同步信号。

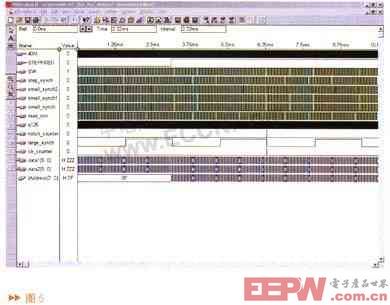

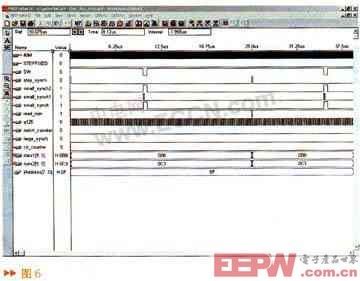

波形文件

在MAX+PLUS II软件开发平台上加以40MHz的激励信号,便可以验证设计正确与否,主要是通过波形文件来验证。波形文件见图5、图6。

结论

把FPGA技术运用在频率综合器中,使用器件少,逻辑功能可重复编程,满足用户后续改变功能的要求,它不改变原来的硬件设计,只需通过修改软件就可实现。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码