采用VHDL设计的全数字锁相环电路设计

2. 3 数控振荡器的设计

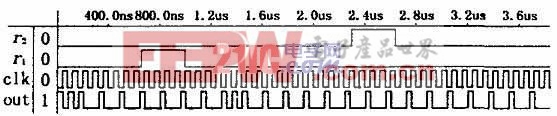

数控振荡器由加/ 减脉冲控制器和除N 计数器组成的。加/ 减脉冲控制器其实是一个增量―减量计数器式DCO。它和环路滤波器连用。如果在环路滤波器无进位、错位的时候,加/ 减脉冲控制器对时钟2NFo 进行二分频。当加/ 减脉冲控制的增量输入端( I = 1) 输入一个进位脉冲时, 输出脉冲中通过该计数器内部加上一个时钟脉冲。反之,当加/ 减脉冲控制的减量输入端( D = 1) 时输入一个借位脉冲输出脉冲中就减去一个时钟脉冲。因此通过借位和进位脉冲可以使输出频率得到改变, 输出频率能被进位和借位脉冲的最高频率控制在一个给定的范围内。加/ 减脉冲控制器由D 触发器和J K 触发器构成,根据功能分析,可以设计出相应的VHDL 程序。其运行后仿真波形如图5 所示:

图5 加/ 减脉冲控制器仿真波形图

3 实验仿真结果与分析

本设计中全数字锁相环路采用软件来实现的,通过用VHDL 语言编写模块,然后仿真,例化,逐渐由下而上的实现整个电路,最终达到整体仿真下载成功。

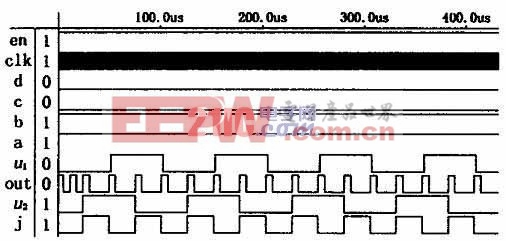

环路锁定( k = 2^5) ,DPLL 系统仿真波形如图6所示。

图6 环路锁定(取k = 2^5) 时的仿真波形

由仿真波形可以看出, u1 和u2 达到锁定状态时的仿真时间是70us。

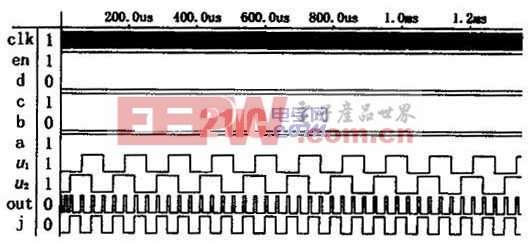

环路锁定( k = 27) 时,DPLL 系统的仿真波形如图7 所示:

图7 环路锁定(取k = 27) 时的波形仿真图

在这种情况下, u1 和u2 达到锁定状态的仿真时间是180ms。

显然,模k 愈大,环路进入锁定状态的时间越长。k 取得过大,对抑制噪声、减少相位抖动有利,但是同时又加大了环路进入锁定状态的时间。反之, k 取得过小,可以加速环路的锁定,而对噪声的抑制能力却随之降低。

4 结语

采用VHDL 设计全数字锁相环路,具有设计灵活,修改方便和易于实现的优点,并能够制成嵌入式片内锁相环。该类数字锁相环路中计数器的模数可以随意修改,这样,就能够根据不同的情况最大限度地、灵活地设计环路。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码