一种SoC芯片在Magma Talus下的物理实现

第四章 时钟树设计

时钟树设计的内容包括时钟树约束的设置、MMMC、OCV(On Chip Variation)及 CPPR (Clock Path Pessimism Removal,或称 Clock Reconvergence Pessimism Removal)的考虑等。

本芯片时钟树设计的难点在于基于latch的时钟门控单元、时钟分频电路以及动态选择电路带来的时钟树平衡问题而导致的时钟树约束的复杂性。

4.1 分离时钟门控单元的时钟树约束

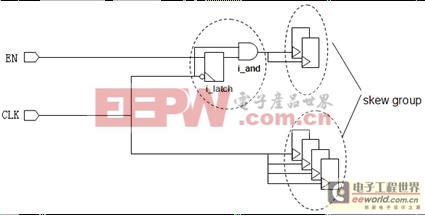

由于PMC模块中存在大量的由latch和and标准单元构成的非集成的时钟门控单元, latch的D端具有endpoint属性,如果不做特殊处理,在时钟树生成时会与其它具有endpoint属性的触发器、锁存器一起进行平衡。这不是我们想要的结果,我们想要的平衡是把latch和and一起构成的时钟门控单元看成一个组合门电路,仅需要其后的触发器和其它没有受时钟门控控制的触发器一起进行平衡,而将latch排除在外。如图6所示:

图6 分离门控时钟电路的skew group

为了达到上述目的,我们将分离分控时钟的latch和and置于一个skew group之内,并将and门的时钟输入端设置为skew anchor。以下面的SoC芯片中的一个分离门控时钟电路为例,约束如下:

force plan clock $m -pin ".../PmcHCLKGate_Inst/i_latch/GN

.../PmcHCLKGate_Inst/i_and/A" -skew_group 49

force plan clock $m -pin .../PmcHCLKGate_Inst/i_and/A -skew_anchor

4.2 分频电路时钟树约束

SoC芯片的PMC模块中分频时钟之间,以及分频时钟和源时钟之间,存在非例外的时钟路径,因此,我们将分频电路时钟域和未分频电路时钟域内的触发器置于一个skew group之内。分频电路本身由于是孤立的逻辑,与其它功能逻辑电路的触发器之间在逻辑上不存在有效数据路径,因此可以单独做成一个skew group。但由于它处于分频时钟域路径上,为使置于同一skew group之内的分频时钟域和源时钟域内的触发器之间的skew在规定的范围内,必须控制分频电路的时钟路径,如图7所示:

图7 分频电路的skew group

我们以某三分频电路为例,下面的命令是对其时钟树创建时的相关约束:

force plan clock $m -pin "…/PmcFHClkDiv3/QQ_reg[0]/CK

…/PmcFHClkDiv3/QQ_reg[1]/CK" -skew_group 54

force plan clock $m -pin "…/PmcFHClkDiv3/QQ_reg[1]/CK" -skew_anchor

force plan clock $m -pin "…/PmcFHClkDiv3/DQ_reg/CKN

…/PmcFHClkDiv3/OR2CLK_Inst/A" -skew_group 55

force plan clock $m -pin …/PmcFHClkDiv3/OR2CLK_Inst/A -skew_anchor

4.3 动态时钟选择电路的时钟树约束

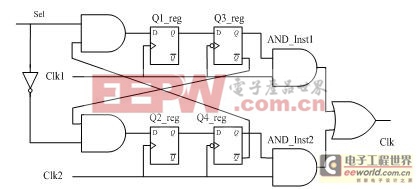

另外,PMC模块中使用动态时钟选择电路用来消除异步时钟间及同步时钟间动态切换过程中的毛刺,其中动态异步时钟选择电路结构如图8所示:

图8 动态异步时钟选择电路结构图

同样,我们针对该电路也做了如下约束:

force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst1/B

…/PmcSysClkSel_Inst/Q1_reg/CK

…/PmcSysClkSel_Inst/Q3_reg/CK" -skew_group 1

force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst2/B

…/PmcSysClkSel_Inst/Q2_reg/CK

…/PmcSysClkSel_Inst/Q4_reg/CK" -skew_group 2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码