基于FPGA的无线同播频率校准装置的设计

2.2 脉冲计时模块设计

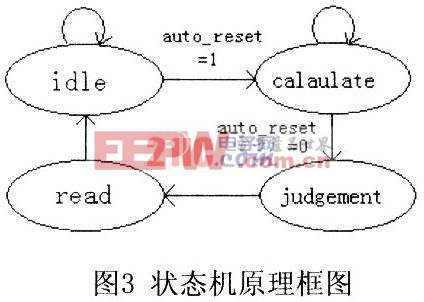

脉冲计时模块接口信号包括:级别输入level[2∶0]、开始计数输入auto_reset、判断输出judge[1∶0]、读指令输出read,还有输入时钟fre_in和复位使能reset,模块内部设寄存器clk_add[32∶0],用于脉冲计数。模块的状态包括idle、calculate、judgment和readtime,状态机如图3所示。

其具体工作过程为:

(1)状态为idle时,read置0,clk add[32∶0]清空,读入level值。Level是计数判断的基准,必须在计数前读入。

(2)当收到auto_reset为高电平,状态从idle转至calculate开始脉冲计数。由于计数的频率同时是FPGA的工作频率,所以clk_add[32∶0]只需在calculate状态下每个时钟累加一次。

(3)auto_reset变为低时,状态转至judgment,将clk_add[32∶0]与所在级别的上下限对比,将结果通过judge[1∶0]输出。

(4)状态转至readtime,将read置1,read信号告知分级控制模块judge[1∶0]信号已经更新,要求读取,当clk_add [32∶0]等于中心脉冲数,read不置为1,表示无需改变电压值。

(5)状态转回idle。

2.3 电压控制模块设计

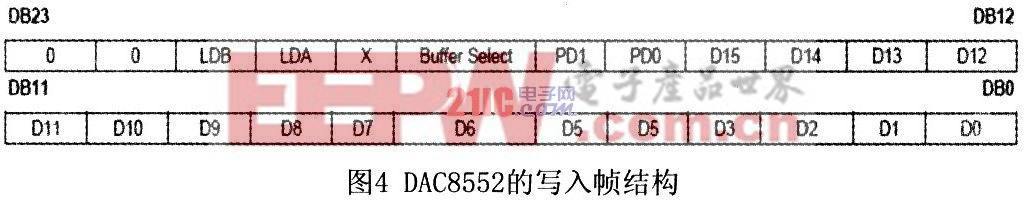

电压控制模块的接口信号包括:级别输入level[2∶0]、调整方向输入step、调整输入load、就绪输出ready、DAC接口输出(sync、SClk和din),还有输入时fre_in和复位使能reset,模块内部设寄存器data reg[23∶0]用于生成控制DAC的帧,max_24bits[4∶0]用于记录当前是控制帧的第几位输出。每帧长度为24位,控制字包括:LDB、LDA选择写入通道,Buffer Select选择写入的寄存器,PDl、PD0选择输出阻抗模式,D15~D0为16位的DAC数据。其帧结构如图4所示。

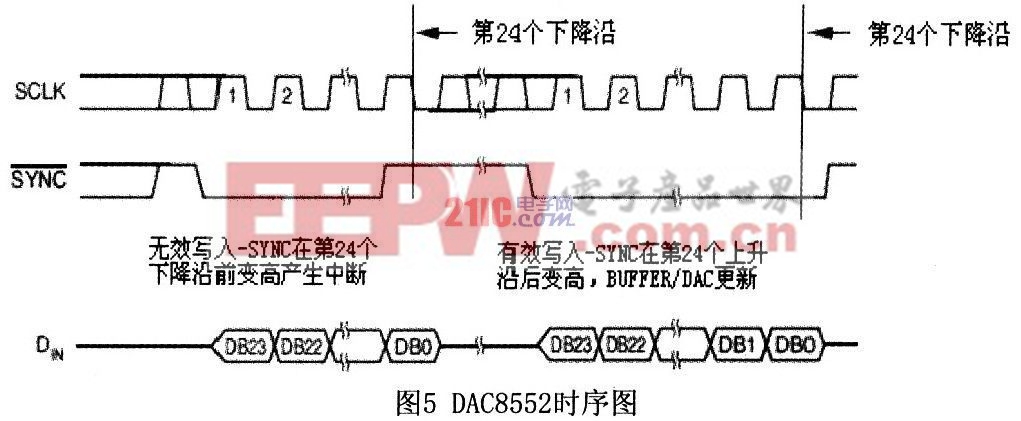

DAC8552采用SYNC、SCLK和DIN三线接口控制方式,从SYNC变低时开始写入,SCLK产生写时钟,在SCLK下降沿数据被写入DAC8552,SYNC必须在第24个下降沿后才重新拉高,否则写入失败。其时序图如图5所示

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码