利用时钟裕度技术实现系统边界稳定性与早期故障预

系统老化

系统老化这是一个老生常谈的问题了,也是一个有趣的问题。世界上没有完美的产品,硅芯片制造也一样。硅芯片的封装会对产品使用寿命产生很大影响,因为封装技术密封性不好,硅芯片会暴露于外界环境。从硅芯片的角度来说,热载流子注入的自然效应与电子移动的细微效果会对系统产生影响。热量会加速硅芯片的老化。老化作为一种灵敏度参数来说,则体现在总时序预算数据上。通过超频与降频对比,发现超频对系统产生的压力最大,这也是性能差分析的基本方法。

时钟裕度的实施

上面谈论了这么多关于时钟裕度技术的话题,那么怎样才能实施时钟裕度技术呢?首先,我们要知道,最先进的系统通常包括众多时钟源。在多数情况下,时钟间存在相互依赖的关系,但有时也会存在独立的时钟。现在,常见的时钟源通常采用锁相环技术,确保噪声最小化,这使得新一代锁相环技术产生的时钟源具有较小的抖动,同时在相位噪声性能方面优于固定的时钟源。锁相环通常作为带可编程分压器的时钟合成器,可支持多种时钟输出的合成,而且相互依赖的不同时钟之间可建立不同的“分频比”。分频比是PC时钟领域的过时术语,但对任何相互依赖的时钟问题来说仍然适用。

为了成功实现时钟裕度功能,其必须内置频率调节的功能。变频功能在实际上可能比最初设想的要更困难,因为我们必须全面了解锁相环技术的性能,不仅要了解工作期间可以实现的目标频率,还要了解不同反馈编程条件下的相位噪声与抖动性能。基于时域的抖动是我们需要了解的重要内容,这样才能确保不同频率之间的一致性(不能突然断开),否则系统的稳定性分析就会出错。如果发生了不连续的抖动情况,也不会出现太大麻烦,可以通过多个特定的输出频率开槽或所需的分频比来解决。此外,应当确保开槽不要在频率变化期间进行,除非锁相环的设置在CPU对任何形式的开槽和短脉冲不敏感的间隔中进行。

确保总时序预算正确的技巧就是,应当了解哪些频率范围表现较好,这样就能小心地通过逐步逼近的办法接近总时序预算目标,而每一步的变化量可能有差别。如果频率变化较大,那么通常会导致总时序预算差别结果较小。总时序预算边界检测要求最终肯定要突破系统的界限,然后重启并略微后退一些,直至获得满意的一致性阈值为止。有许多没有文件记载的“小窍门”可以完成此项工作。建立系统总时序预算的关键就是一致性与可重复性。

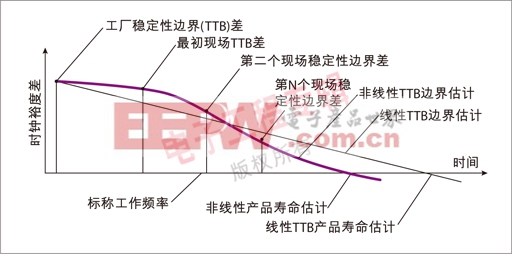

正如前面简单谈到的那样,执行时钟裕度工作所发现的最重要信息就是在产品投入使用后估算出实际的产品使用寿命终结时间。本文分析的目的就是要通过时钟裕度来计算产品的标称性能与总时序预算之间的差异,以备后续之需。在几周、几个月乃至几年的时间里,投入实际使用的产品运行相同的回归进程,重复计算性能差异。我认为,能够体现产品使用寿命结束的情况就是在性能差为零或为负值。这并不是说系统出现故障,而只是说没有性能差了,说明产品已经到了使用寿命的终点。无论采用何种产品支持方式,如果性能差为零,则说明产品的使用寿命已经结束了,这一信息对那些需要全天候持续工作的系统来说是至关重要的。如图1所示,根据历史性能差信息预测出了性能差为零的时间。通过简单的线性分析或非线性曲线分析,可以估计得出产品使用寿命结束的时间。

图 1:系统使用寿命估算分析图。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码