基于AIS的船舶避碰系统研究

3.2 DSP和FPGA的接口设计

比较Altera公司的多个系列的FPGA产品,本设计选取CycloneⅡ系列的芯片EP2C35F672。它主要具有以下特性:嵌入式存储资源支持各种存储器应用和数字信号处理(DSP)实施的要求,引脚数量充裕有160个,可提供100个I/O用户引脚,且I/O具有三态缓冲、总线状态保持等功能,该芯片由128 MB FLASH内存和8 MB SSRAM存储区和两个串口。它可以满足本系统所需的数据采集控制和串行口复用等功能。接口电路如图3所示。

在上述设计中AIS信息的串口直接接到DSP芯片上,是为了避免直接应用多串行口中断共享方式可能会不可靠。原因是假如在服务串行口A时上一次检测过的串行口B发生了中断,此时中断服务程序如果直接退出,则中断B就未被服务。这种情况下,CPU可能会再次进入中断服务程序,多次进出中断必然造成处理器资源的浪费。更糟糕的是退出中断服务程序时,由于DSP中断标志位已经被清除且DSP中断引脚保持高电平,此时中断就不会再被标志,造成中断死锁导致外部中断根本无法继续工作。为确保DSP芯片及时接收到AIS信息,为AIS单独留下专用串口。

3.3 DSP和FPGA与其他外围电路的接口设计

船舶避碰系统中设计了基于同一片FPGA上的液晶显示接口和键盘接口,使避碰系统具有更强的功能。键盘接口利用FPGA内的硬件资源设计,在不影响DSP进行船舶避碰算法运算的条件下,用于船舶避碰系统的调试和控制。

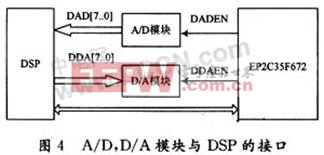

同时完成了A/D、D/A模块的接口设计。模拟信号经过前置滤波、放大,再通过多路模拟开关和A/D转换器转换成数字信号进入FPGA,A/D、D/A模块与DSP的接口电路如图4所示。

4 结 语

本文研究的内容为基于AIS的船舶避碰系统,涉及到信息的解码过程,利用DSP作为系统的微处理器和FPGA作为接口的扩展与协调,根据接收的信息,进行船舶避碰算法的运算。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码