无需缓冲器的反激式转换器技术

利用这些假设,RCD箝位的功耗可以表示为存储在电感器中的能量,具体如下:

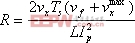

公式2

公式2

换句话说,我们让开关上的箝位电压升得越高,总功耗越低。但是当然,我们必须对此进行平衡以防止总电压出现在功率FET两端,因此我们不能任意降低功耗。

一个典型设计可用于电压vx等于1/2反激电压。在这种情况下,功耗等于存储在漏感中能量的三倍,它不是一个立即可见的结果。然而,这是一个保守的估计。它没有解释电感器的有损放电,也没有解释杂散电容。实际上,由于这些结果,该设计的箝位损失将比预期的更少。

高压离线设计这些经常限制使用一个最高电压为650或700V的FET,电压vx将将很难限制所设定的最大输入电压、最大电流和FET击穿电压。不要超过FET规定的Vds,意识到击穿可能随温度变化。一些设计人员依赖于FET的雪崩能力,让它有规律地超过击穿电压。这不是为可靠的电源设计推荐的。

设计步骤3――选择箝位电阻器

缓冲器的电容器需要足够大,以保持一个相对恒压,同时吸收泄漏能量。除了这一考虑,其逻辑值要求不高,当缓冲器正常工作时不会影响峰值电压。

电阻器在确定峰值电压vx方面是至关重要的元件,因此需要根据以下公式选择:

公式3

公式3

一个大数值电阻器将减缓箝位电容器的放电,有助于电压提升到更高值。一个小数值电阻器将导致较低的箝位电压,而功耗将增加。

设计步骤4――计算功率损耗

现在缓冲器设计已经完成,但是我们经常还需要知道上述公式中,除了最差条件电流Ip,电流的功耗是多少。使用以下公式计算某一给定峰值电流I和漏感L的已知缓冲器的电压上升。

vx是电压上升值,高于反激电压,可以表示为:

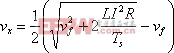

公式4

公式4

功耗可以表示为:

公式5

公式5

设计步骤5――实验验证

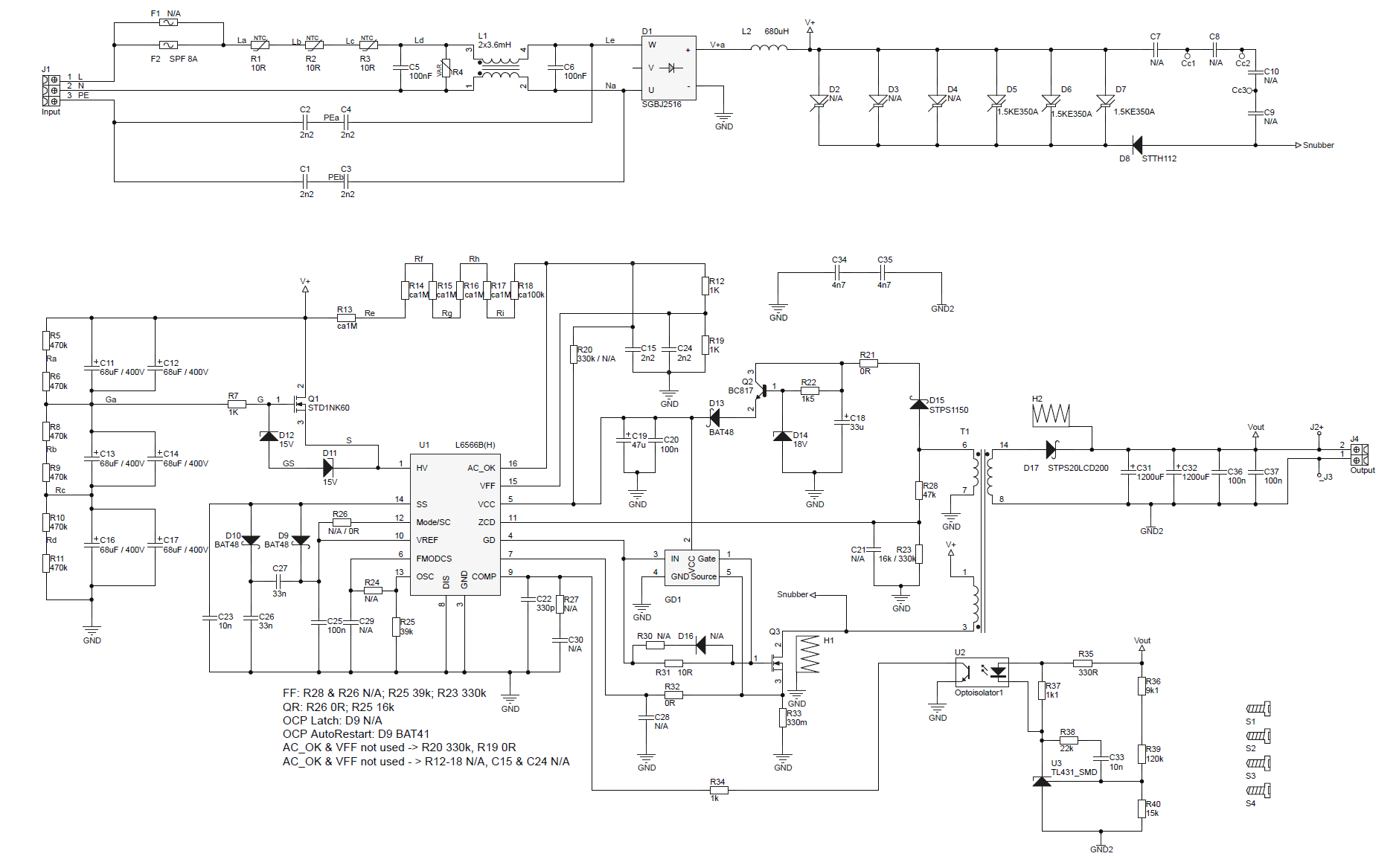

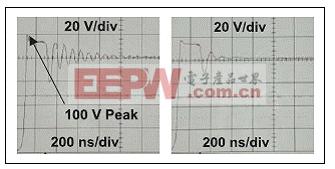

设计的实验验证是必不可少的,因为将出现没有计入公式的结果,你的电路将出现非理想的元件。图3所示为箝制FET漏极电压峰值电路的效益。

图3. 带有初级RCD箝位的反激式转换器漏极电压。

该数值还给出了一个RCD箝位限制。在箝制周期结束之后,电路恢复振铃。采用理想的元件,这将不会发生。不过,RCD箝位的二极管有一个有限的反向恢复时间,有助于漏感电流流入二极管的相反方向,可导致振铃。RCD缓冲器各种类型二极管选择至关重要。它必须尽可能的快,具有合适的额定电压。

这个振铃的严重程度将取决于RCD二极管两端反向施加的电压。你允许的箝位电压爬得越高,功耗就越低,电压越高且dv/dt施加在二极管上,振铃将增加。

通过采用RC缓冲器随后的振铃可以再一次被抑制。

总结

RCD箝位电路对所有反激式转换器非常有用,可以减少功率FET上的压力。要确保箝位的目的是将最差工作条件下(高电压和最大电流极限)的电压限制低于元件的额定电压。本文中的设计公式排除了来自箝位设计的猜测。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码