基于Actel FPGA的PWM IP的应用

(2) PWM的优点

PWM的优点是从处理器到被控系统信号都是数字形式的,无需进行数模转换。让信号保持为数字形式可将噪声影响降到最小,噪声只有在强到足以将逻辑1改变为逻辑0或将逻辑0改变为逻辑1时,才能对数字信号产生影响。这也是在某些时候将PWM用于通信的主要原因,从模拟信号转向PWM可以极大地延长通信距离。在接收端,通过适当的RC或LC网络可以滤除调制高频方波并将信号还原为模拟形式。

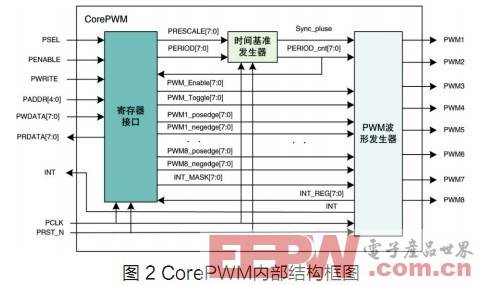

(3) CorePWM的结构框图

CorePWM的内部结构框图如图 2所示。它主要由时间基准发生器、PWM波形发生器和寄存器接口等模块组成。

● 时间基准发生器:接收PRESCALE和PERIOD寄存器的值,并产生一个0~255的周期计数。

● PWM波形发生器:用输入周期计数器和上升、下降沿寄存器的值进行比较,当计数值等于任何一个边沿寄存器的值的时候,就会产生一个相应的PWM波形输出,并且中断寄存器将会被更新。

● 寄存器接口:主要是提供PWM内核的APB总线协议的接口。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码