基于软件无线电思想的数字通信终端接口电路设计与实现

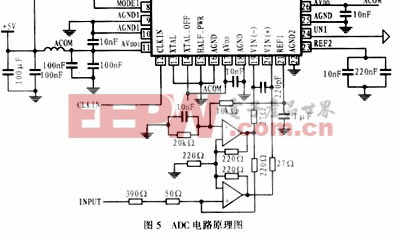

3.2 ADC的电路

虽然话音信号的带宽是位于中频部分(20kHz~200kHz),相对较宽(200kHz),但其中夹杂着大量的带内噪声,因此必须使用一个高速ADC(根据那奎斯特第一采样定理,该ADC的采样速率必须达到500ksps,同时为了提供一定的冗余量,本系统选取的ADC芯片的最高输出采样速率也应达到1.2Msps)来将模拟信号转换为数字信号。另外,片内采用Σ-Δ调制的ADC也能对带内噪声起到良好的抑制作用,这种拟制主要通过对带内噪声整形及片内滤波器来实现,所以,高速采样Σ-Δ调制ADC是本系统的首选。

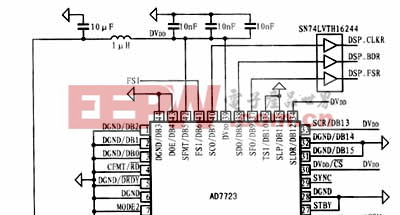

系统中的高速ADC可选择分辨率为16位的Σ-ΔADC芯片AD7723。该器件的过采样率有32/16×Fs可供选择(本系统采用32×Fs的过采样率)。它采用单+5V电源,片内参考为2.5V;并具有并行输出和串行输出两种方式,在输出字速率达1.2MHz的情况下,其输入信号的带宽可达 460kHz,同时能向DSP(TMS320VC5410)的McBSP提供时钟信号、帧同步信号和数据流信号,因此,该高速ADC能够和DSP组成高速数据采集系统。图5是其电路连接图。

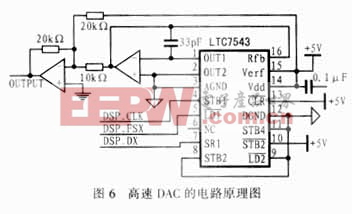

3.3 DAC电路

高速DAC可选用分辨率为12位的LTC7543,该芯片的信号转换稳定时间(settling time)典型值为0.25μs,最大值为1μs。LTC7543采用+5V单电源供电并具有和DSP(TMS320VC5410)的McBSP相兼容的时钟信号、帧同步信号和数据流信号输入引脚,输出信号可采用双极性输出,也可以采用单极性输出(本系统采用前者)。LTC7543的外围电路比较简单,图 6是其电路连接图,它由两个宽带运放,一个外部参考电压,一个电源滤波电容,一个输出滤波电容和若干电阻组成。

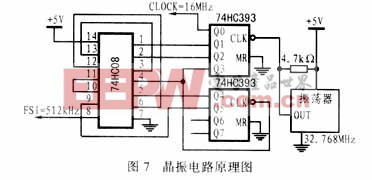

3.4晶振电路

晶振电路选用的主要器件如图7所示,该电路包括32MHz的有源晶体振荡器、74HC393二进制分频器和74HC08逻辑与门。其中 74HC393用来产生高速ADC的时钟输入信号和帧同步信号;74HC08用来调整帧同步信号的脉宽,以使其与时钟信号的脉宽大小一致。

4结束语

以上所选的主要器件组成的电路均已做成PCB(印刷电路板),并通过信号测试。测试结果表明:窄带带通滤波器(N_BPF1、N_BPF2)的阻带衰减为 40dB;宽带带通滤波器(B_BPF1、B_BPF2)的阻带衰减为60dB;同时通过高速ADC完全可以实现对500kHz模拟信号的采样、量化和编码。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码