基于FPGA的航空总线协议接口设计

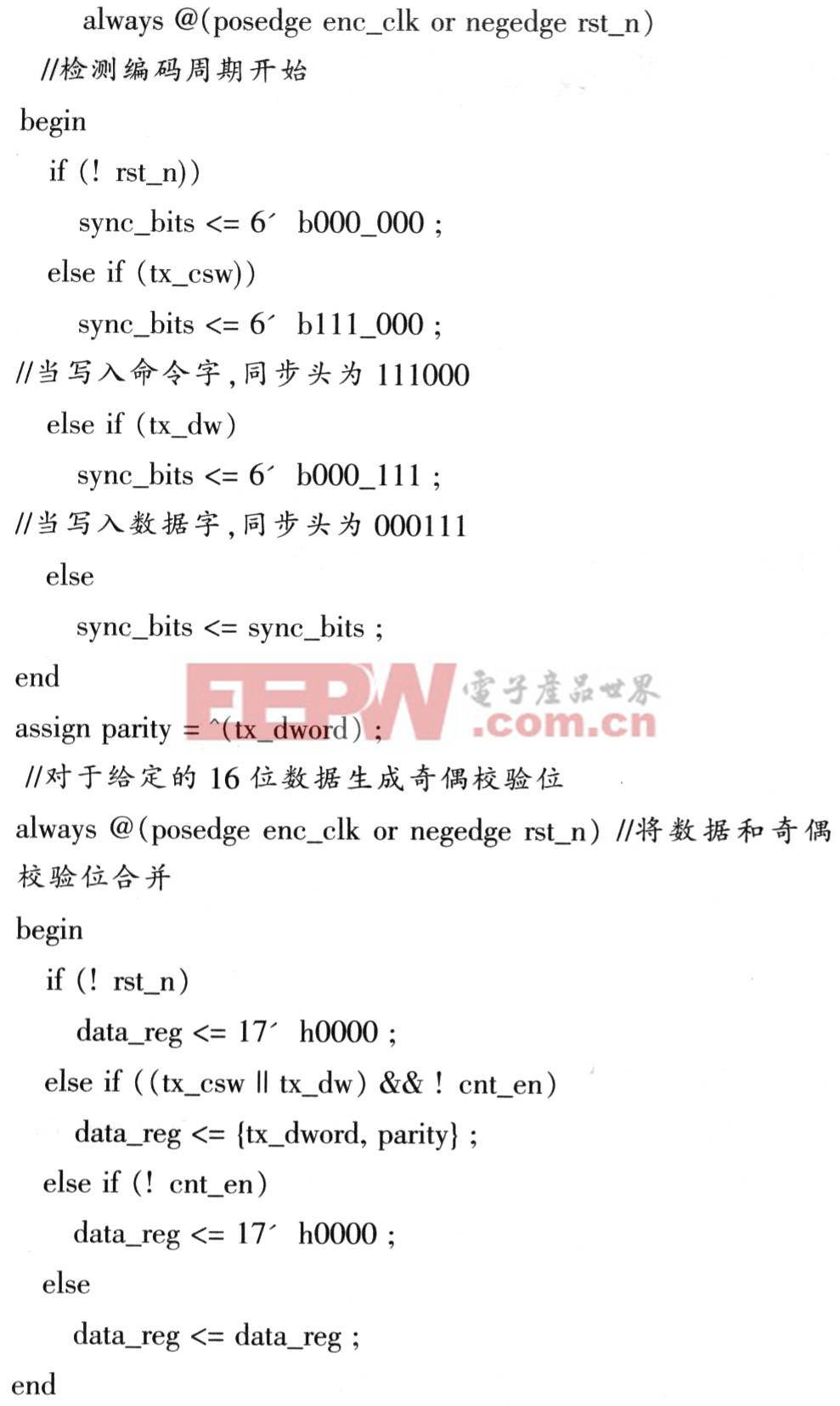

下面给出部分编码模块的源代码:

解码模块也可分为同步字头检测、数据解码、串并转换与奇偶校验3部分。这个过程与编码模块相类似。

4.2 消息处理模块

消息处理模块主要是接收来自PC机的命令,并且将其运行结果上传至PC机。为了能够快速开发系统,采用EDK自带的串口控制器IP Core。由于在Virtex-II Pro开发板上已设计与PC机相连的RS-232串口,并且配有标准的DB-9接口,因此只需通过IP Core 16450-UART控制器接收和发送数据即可实现系统与PC机的消息处理功能。

5 实验结果

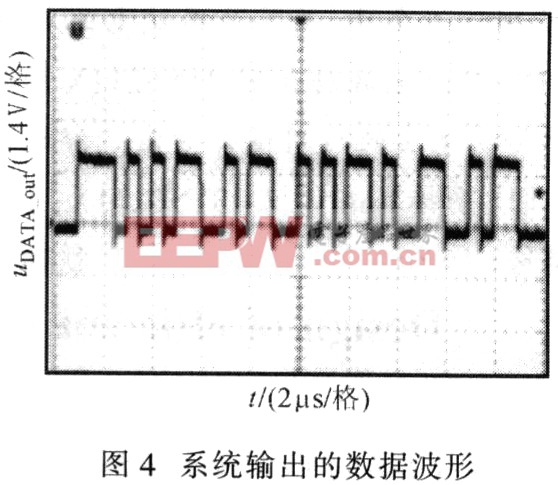

通过发送已知数据和示波器观察实际接收到的数据波形,进行系统测试。测试中,输入的十六进制数据为1234H,通过Tektronix公司的TDS3032B型示波器测试输出数据,图4是测得的系统输出的数据波形,其中,波形前3位表示同步字头,先负后正,表示发送的是数据字,正负电平各占1.5μs,中间的16位曼彻斯特码恰好等于发送的1234H,而最后1位数据为奇偶位。因此测试结果证明:该系统设计能够正确接收和发送符合1553B总线接口协议的数据,且工作稳定可靠。

6 结语

采用基于SoPC的设计方法,完成了MIL-STD-1553B航空总线接口逻辑的开发,并利用仪器测试系统。将该系统设计的总线协议接口逻辑固化到FPGA中。可取代国外进口的专用1553B总线控制器器件,从而摆脱长期依赖于国外进口器件的束缚,具有良好的军事和经济效益。该系统的创新之处是采用先进的SoPC技术开发FPGA,全面实现1553B总线接口逻辑,系统具有配置灵活,易于扩展等特点。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码