智能卡抗DPA攻击的设计与实现

对于智能卡的DPA攻击,主要是利用在卡上嵌入式微处理器运作时,某个特定指令的执行或数据存取所消耗功率,在供应电压源上所表现特定的电流频谱提供的有用信息。故可以通过外加额外的电路造成额外的电流消耗,从而改变电流频谱以达到抗DPA攻击。同时额外的电流消耗电路必须通过采用随机数随机的方式,产生随机数消耗电流,以达到芯片消耗电力无法预测性,使其不能被分析与统计。

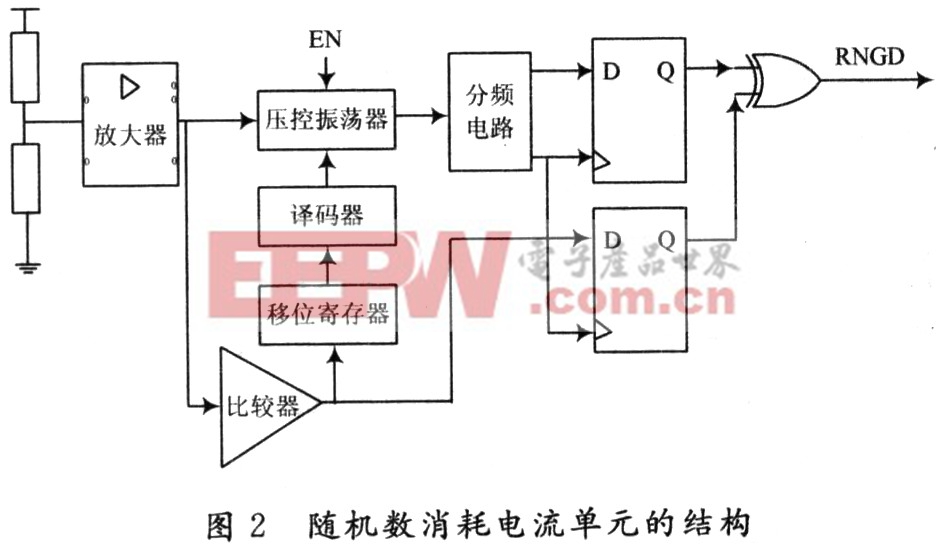

为此,可以在随机数产生电路中设计如图2所示的随机数消耗电路,电路由比较器、移位寄存器、译码器组成;当电阻噪声产生的噪声电压经过放大器、比较器后,产生“1”或“0”数字信号,存入移位寄存器,这样寄存器内的值已经类似混沌式RNG所产生的随机数,此随机数经译码器编码后,控制三态充放电缓冲器的充放电个数,最终达到以随机数控制电流消耗的目的。

3.2 组合逻辑防DPA攻击设计

防DPA攻击的主要目的是使电路特性在运算时保持相同,而保持电特性相同很重要的一点是使翻转的晶体管数量在任何运算步骤中都是一个常数。为实现这个目的可在电路运算步骤之间增加一个中间步骤,这样能防止有用信息从功耗分析中泄漏出去。最简单的中间步骤设置是在输入参数和电路运算完成之后设置系统中间值。

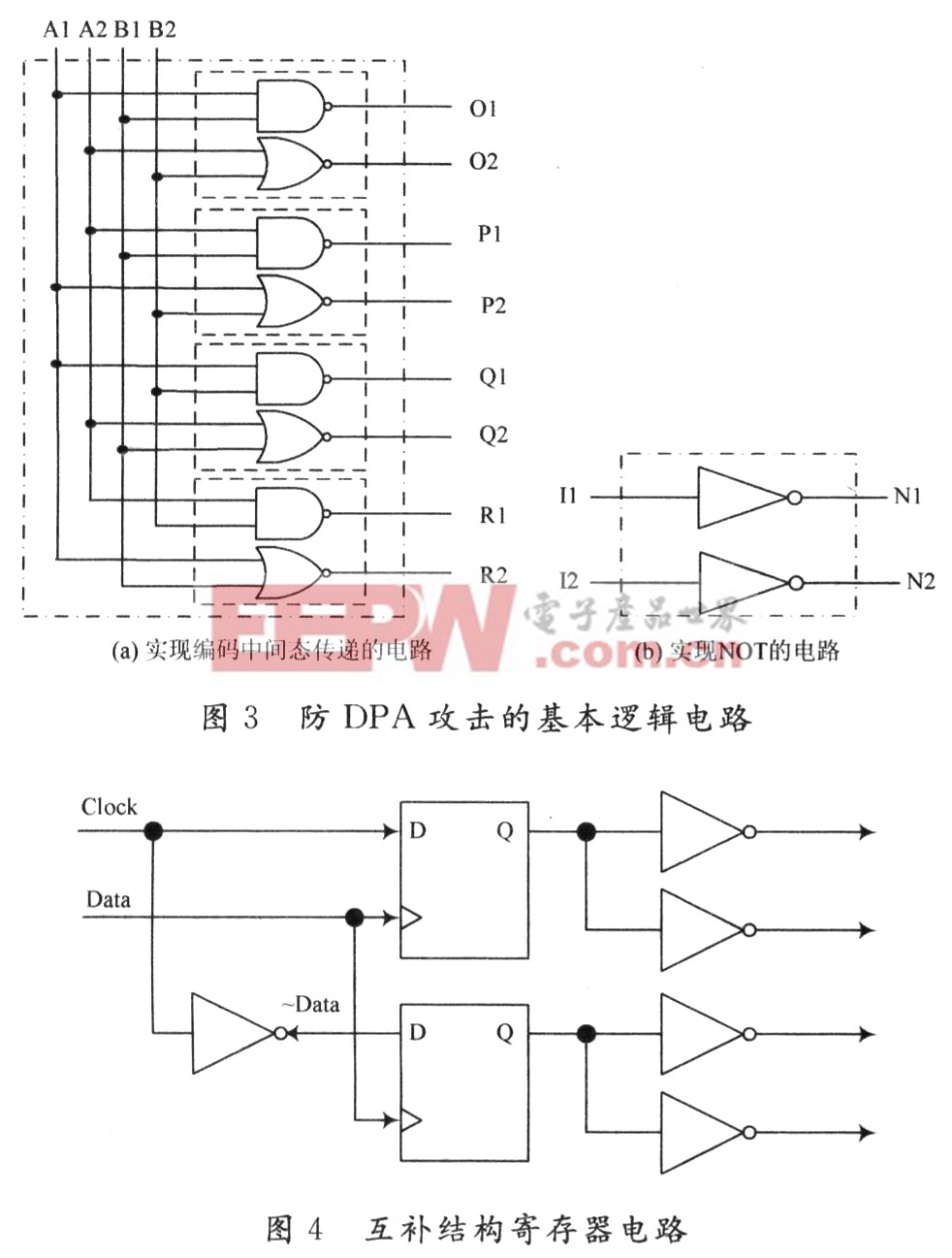

为此,参考异步逻辑电路的双轨编码方式中对信息的每一位用两根信号线进行编码的方式。采用两位信号线的组合值“01”和“10”来表示数字逻辑的“真”和“假”,而组合值“00”和“01”则为中间值。这样的编码方式下,设计的基本逻辑单元电路如图3所示。

如图3(a)电路对于输入A(A1A2)和B(B1B2),输出只有O1O2和R1R2有效,当输入A1A2B1B2为0000或1111时,输出O1O2和R1R2的值是11或00,这样实现了编码中间态的传递。而当输入A1A2B1B2为有效数据0101,0110,1001和1010时,输出O1O2和R1的值就得到相关的NAND,AND,NOR和OR四个逻辑功能;其中,输出O1O2→NAND,O2O1→AND,R1R2→NoR,R2R1→OR。至于NOT的实现如图3(b)的电路所示。所以,上述基本的逻辑电路足以实现复杂的数字组合逻辑运算功能。

3.3 时序逻辑防DPA攻击设计

针对差分功耗分析,除了利用增加电路噪声以降低差分功耗分析的信噪比的防御方案外。通过减小差分功率信号的值,同样可以降低差分功耗分析的信噪比;若电路不同状态下的功率差异趋于零,则差分功耗分析将失效。于是基于上述思路,在时序逻辑电路设计上可采用如图4所示的互补结构寄存器电路。

设寄存器初始状态相同,输出负载相同,时钟沿赋值,如图4不论输入为O或1,两个互补寄存器必是一个翻转,另一个不翻转,因此总的功耗在两种情况下没有差别。

另外,对于采用前面所述的双线信号编码方式,在时序逻辑电路的设计上,可采用在输入任何有效的数据01和10之前,都先把寄存器设置为00或11中间态的协议。这样,无论进行何种操作,则时序逻辑中相关的寄存器都只有一个寄存器翻转,有效地防止了寄存器在数据传输过程中的信息泄漏。

4 结 语

智能卡是一种高安全性、高可靠性和复杂的片上系统,具有抗功率分析攻击、时间分析攻击和故障分析攻击的能力,但在一些新型的智能卡攻击技术下其安全受到巨大的挑战,例如DPA攻击。本文针对DPA攻击智能卡的特点,在智能卡的硬件电路上进行了抗DPA攻击的设计,采用此设计,再结合一些软件上的抗DPA攻击措施,就能构成一个完善的智能卡安全体系结构,能十分有效地保证智能卡免受DPA攻击。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码