用内部逻辑分析仪调试FPGA(08-100)

推动FPGA调试技术改变的原因

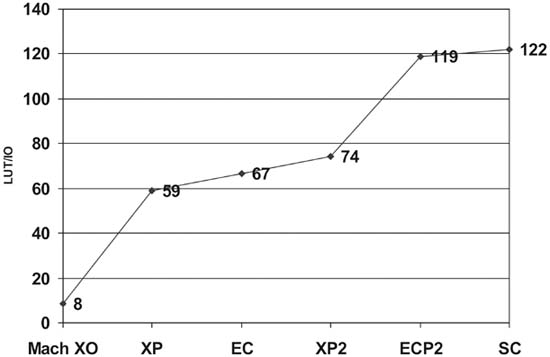

进行硬件设计的功能调试时,FPGA的再编程能力是关键的优点。CPLD和FPGA早期使用时,如果发现设计不能正常工作,工程师就使用“调试钩”的方法。先将要观察的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。然而当设计的复杂程度增加时,这个方法就不再适合了,其中有几个原因。第一是由于FPGA的功能增加了,而器件的引脚数目却缓慢地增长。因此,可用逻辑对I/O的比率减小了,参见图1。此外,设计很复杂时,通常完成设计后只有几个空余的引脚,或者根本就没有空余的引脚能用于调试。

图1 Lattice FPGA的LUT/可用I/O

第二,现在设计的复杂性经常需要观察许多信号,而不是几个信号。常用的技术是实现较宽的内部总线,以便在较大的FPGA中达到高的系统吞吐量。如果怀疑内部的32位总线里有坏的数据,则难以用几个I/O引脚来确定问题所在。

第三,通常需要在系统中测试复杂的功能。在这种情况下,在系统中调试时访问一些I/O也许是有限的。新类型的包还限制访问FPGA引脚。系统速度也是个问题,因为探针的连接可能会引起性能或者噪声信号降低。

最后,推动FPGA调试方法改变的关键因素是有了新的工具,这些工具采用 内部或者嵌入式逻辑分析仪。

拥有这些工具可得到最佳的结果,而不是用与先前工具相同的方法。资源、静态参数和动态参数通常约束了内部逻辑分析仪和外部逻辑分析仪。本文对这两种类型工具的约束进行了比较,考察如何最佳地利用内部逻辑分析仪。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码