基于ADSP-TS201S的图像采集处理系统(05-100)

DSP处理器阵列模块中DSP2和DSP3是用来实现图像处理中的主要算法。DSP2和DSP3分别用链路口与DSP1连接,接收由DSP1传送来的数据,DSP2和DSP3也分别用链路口连接DSP4,通过链路口将处理的数据传送给DSP4,进行下一步处理和数据整理。另外,DSP2和DSP3也直接采用链路口连接,实现DSP2和DSP3之间的通道,从而可以方便地将DSP2和DSP3配置成流水线或并行处理模式。

DSP处理器阵列模块中DSP4接收DSP2和DSP3发送来的数据,进行进一步处理后,将最后处理的数据通过数据总线发送到双端口RAM,通过PCI接口芯片PCI9054,将数据发送给PC机。该双端口RAM采用3片IDT70LV27(32K x 16-Bit),组成96K x 16-Bit方式,保证一次写完一帧(320×240个象素,每个象素两个字节),当DSP4写满一帧图像数据后,向PC机产生中断,请求PC机将数据读走,当PC机读取完一帧图像数据后,应提供相应的应答,允许DSP4刷新双口RAM。DSP阵列机互连电路如图1所示,DSP4与双口RAM的连接如图4所示。DSP4接3片双口RAM,与PCI9054形成接口。DSP4的FLAG0作为通过PCI9054输出的视频传输握手信号。

ADSP-TS201S阵列机采用链路口互连方式,在主要的数据传输方向设置了数据传输启动FLAG信号到接收方的IRQ产生中断,以便更好的实现时序的匹配。

DSP1引入了工作/关闭选择(FLAG1输入),数据模式(数字/模拟)选择由DATA14引脚读入,可以在一帧数据开始输入时,读入一次数据选择模式,此后就可以不再处理了。

图4 DSP4与双口RAM接口

·PCI接口模块

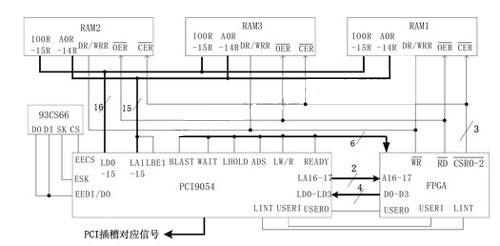

PCI接口采用PLX公司的PCI9054接口芯片,32位,33MHZ数据总线。RAM1,2,3三片双口RAM(IDT70LV27)作DSP4数据输出缓存。由PCI9054读入到PC机。在双口RAM内,相当于右半边接口,PCI9054其电路连接如图5所示。PCI9054对应着PCI槽的信号,按PCI槽名称对应连接,加载EEPROM选用93CS66。 将LD0~LD3引入到FPGA内,可以单次I/O写方式,输出4位状态,作主机控制。开、关机,数字视频/模拟视频选择以A16~17的译码之一作地址选择。FPGA读入后,译码成控制信号输出。

图5 PCI9054与双口RAM,FPGA连接

结语

基于ADSP-TS201S的图像采集处理系统能够完成图像的高速处理,实现图像的实时显示,目标跟踪。在实际应用中该系统工作稳定,达到预想效果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码