选择正确的串行总线系统(05-100)

传统并行总线结构已很好地服务于网络、通信、服务器和存储设备设计人员20多年。标准基总线,从VME和PCI到最近的Compact PCI 和PCI-X,为数据传输提供一贯地可靠、可扩缩、经济的机构。

现在,这些方案已达到其性能极限。随着处理器和I/O器件速度的提高,需要更高速度的系统总线来连接这些器件。

然而,只有两种方法能促进并行总线性能:增加时钟率或加宽总线。定时歪斜问题和线阻抗、信号负载和线迹路由对信号歪斜的贡献可增加功耗和增 多I/O引脚数,从而增加成本。

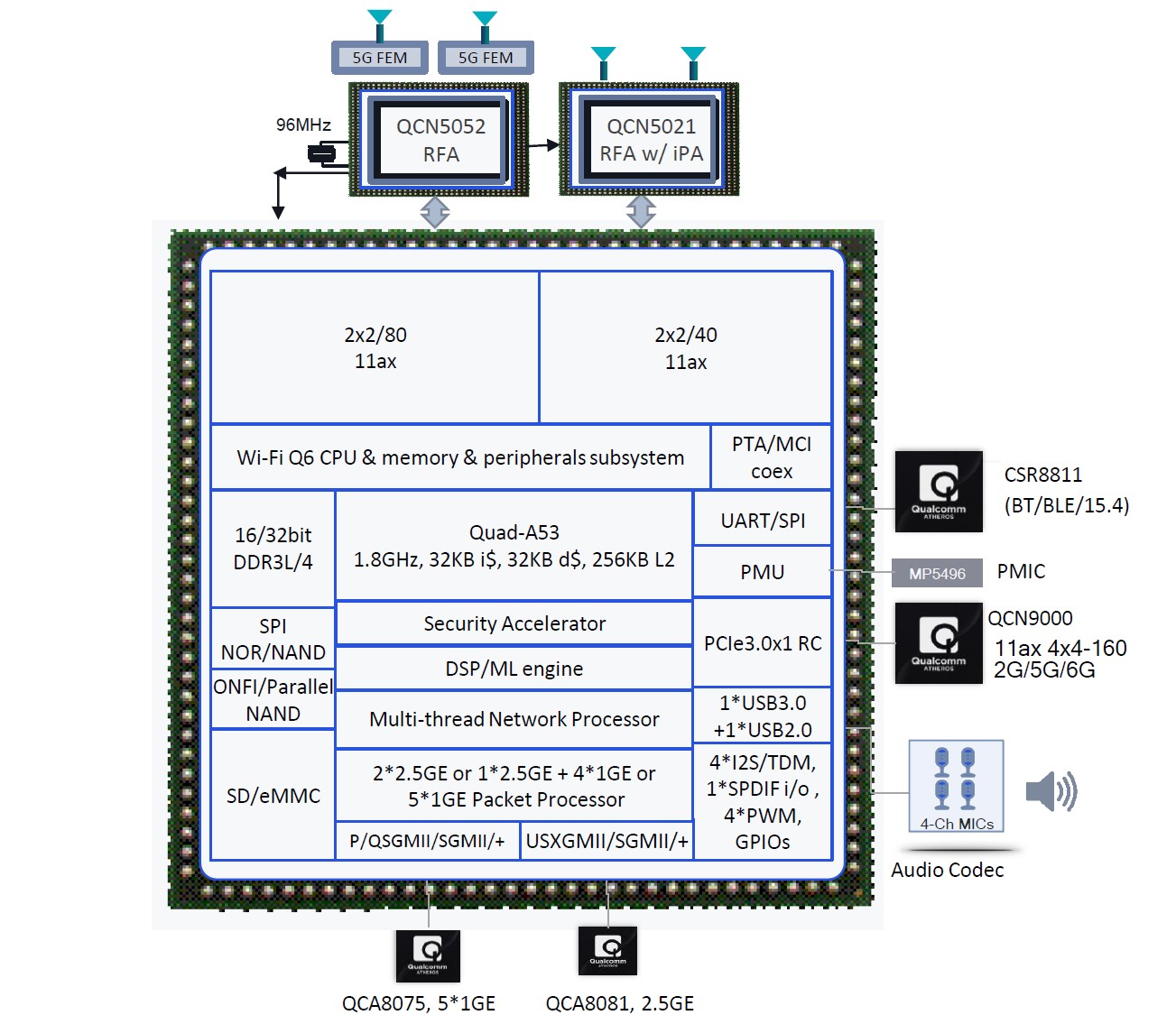

现在,业界已转向不同的串行总线标准来设计较高带宽的系统。靠消除数据和时钟线之间的歪斜,这些自定时总线结构支持每个引脚更快的数据率和更高带宽。

业界已不选择围绕聚集专门串行总线技术用于所有的应用。替代方法是开发人员为不同的应用精巧设计不同串行互连标准。每种技术具有自己本身的性能特点、成本结构、管理能力以及服务和可靠性级别。每种技术也为扩展提供截然不同的机会。

对于大量的有线和无线通信应用,设计人员必须加载有关的千兆位Ethernet和先进的开关互连(ASI)标准。从成本及容易使用的观点来看,广泛采用的千兆Ethernet标准,提供一个有吸引力的解决方案。大多数设计人员都熟悉Ethernet,它的巨大生产规模使其成本此其他方案要低。

然而,它有限的性能,也限制了它的应用范围。此标准不能支持载波类服务质量(QoS)或提供性能保证。有限的Ethernet开关能力,限制了它的通信管理能力以及不可靠性问题。它允许降低信息包,对于端对端可靠性采用效率低的TCP/IP层,而且提供最低的流控制能力。

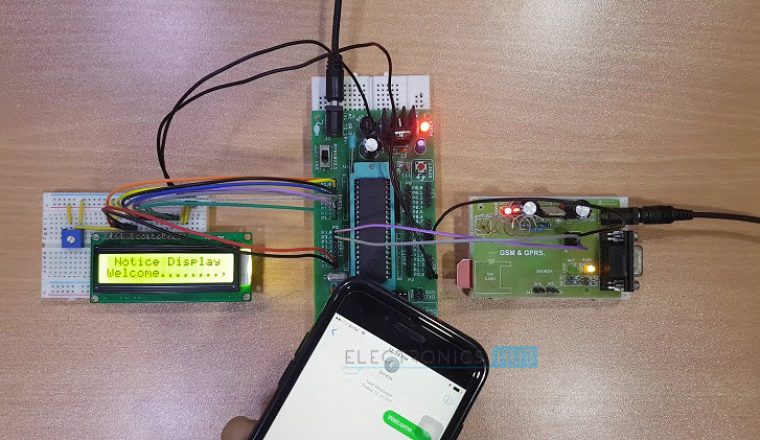

图1 设计ASI支持载波类性能

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码